FREE NEWNES ONLINE MEMBERSHIP

# DIGITAL SIGNAL PROCESSING

Everything you need to know to get started

- Understand how to design and develop DSP from first steps: no previous experience required

- Visualize, practice and implement DSP with stepby-step instructions, illustrations, worked examples and online applets

- Breaks down the complex design and development of DSPs into easy-to-learn building blocks – without complex or involved math!

## Michael Parker

## **Digital Signal Processing**

Everything you need to know to get started

Michael Parker Altera Corporation

AMSTERDAM • BOSTON • HEIDELBERG • LONDON NEW YORK • OXFORD • PARIS • SAN DIEGO SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO Newnes is an imprint of Elsevier

#### Newnes is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA The Boulevard, Langford Lane, Kidlington, Oxford OX5 1GB, UK

#### © 2010 ELSEVIER Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher. Details on how to seek permission, further information about the Publisher's permissions policies and our arrangements with organizations such as the Copyright Clearance Center and the Copyright Licensing Agency, can be found at our website: www.elsevier.com/permissions.

This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods, professional practices, or medical treatment may become necessary.

Practitioners and researchers must always rely on their own experience and knowledge in evaluating and using any information, methods, compounds, or experiments described herein. In using such information or methods they should be mindful of their own safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors, assume any liability for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the material herein.

#### Library of Congress Cataloging-in-Publication Data

Parker, Michael, 1963 Digital signal processing 101: everything you need to know to get started / Michael Parker. p. cm. Includes bibliographical references and index. ISBN 978 1 85617 921 8 (alk. paper) 1. Signal processing Digital techniques. I. Title. TK5102.9.P385 2010 621.382'2 dc22

#### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library.

For information on all Newnes publications visit our Web site at www.elsevierdirect.com

10 11 12 13 14 10 9 8 7 6 5 4 3 2 1 Printed in the United States of America

2010002121

### Introduction

This book is intended for those who work in or provide components for industries that are made possible by digital signal processing, or DSP. Sample industries are wireless mobile phone and infrastructure equipment, broadcast and cable video, DSL modems, satellite communications, medical imaging, audio, radar, sonar, surveillance, electrical motor control—this list goes on. While the engineers who implement these systems must be very familiar with DSP, there are many others—executive and midlevel management, marketing, technical sales and field engineers, business development, and others—who can benefit from a basic knowledge of the fundamental principles of DSP.

Others who are a potential audience include those interested in studying or working in any of these areas. High school seniors or undeclared college majors considering a future in the industries made possible by DSP technology may gain sufficient understanding that enables them to decide whether to continue further.

That, then, is the purpose of this book: to provide a basic tutorial on DSP. This topic seems to have a dearth of easy-to-read and understand explanations. Unlike most technical resources, this is a treatment in which mathematics is minimized and intuitive understanding maximized. This book attempts to explain many difficult concepts like sampling, aliasing, imaginary numbers, and frequency response using easy-to-understand examples. In addition, there is an overview of the DSP functions and implementation used in several DSP-intensive fields or applications, from error correction to CDMA mobile communication to airborne radar systems.

So this book is intended for those of you who, like me, are somewhat dismayed when presented with a blackboard (or whiteboard) full of equations as an explanation on DSP.

The intended readers include those who have absolutely no previous experience with DSP, but are comfortable with high-school-level math skills. Many technical details have been deliberately left out, in order to emphasize just the key concepts. While this book is not expected to be used as a university-course-level text, it can initiate readers prior to tackling a proper text on DSP. But it may also be all you need to talk intelligently to other people involved in a DSP-centric industry and understand many of the fundamental concepts.

To start with, just what is DSP? Well, DSP is performing operations on a digital signal of some sort and using a digital semiconductor device. Most commonly, multipliers and adders are used. If you can multiply and add, you can probably understand DSP. Actually, signal processing was around long before digital electronics. Examples of this are radios and TVs. Early tuners used analog circuits with variable capacitors to dial a station. Resistors, capacitors, and vacuum tubes were used to either attenuate or amplify different frequencies or to provide frequency shifting. These are examples of basic signal processing applications. The signals were analog signals, and the circuits doing the processing were analog, as was the final output.

Today, most signal processing is performed digitally. The reason is that digital circuits have progressively become cheaper and faster, as well as due to the inherent advantages of repeatability, tolerance, and consistency that digital circuits enjoy compared to analog circuits.

If the signal is not in a digital form, then it must first by converted, or digitized. A device called an analog-to-digital converter (ADC) is used. If the output signal needs to be analog, then it is converted back using a digital-to-analog converter (DAC). Of course, many signals are already digitized and can be processed by digital circuits directly.

DSP is at the heart of a wide range of everyday devices in our lives, although many people are unaware of this. A few everyday examples are cellular phones, DSL modems, digital hearing aids, MRI and ultrasound equipment, audio equipment, set top boxes, flat-screen televisions, satellite communications, and DVD players.

As promised, the mathematics will be minimized, but it cannot be eliminated altogether. Some basic trigonometry and the use of complex numbers are unavoidable, so an early chapter is included to introduce these concepts, using as simple examples as possible. There is also one appendix section where very basic calculus is used, but this is not essential to the overall understanding.

## Acknowledgments

This book grew out of a need for Altera marketing and technical sales people to have an intuitive-level understanding of DSP fundamentals and applications, in order to better work on issues that our customers face as they implement DSP systems. I am grateful to the Altera management for the support this book has received, in particular from Steve Mensor and Chris Balough.

My understanding of the topics in this book is based on many years of engineering implementation work and collaboration and explanations from many of my colleagues at multiple firms over the years. More recently, within Altera, many people have contributed to my knowledge in these areas. I would like to especially acknowledge a few people who have been helpful both in DSP domain and relevant applications and implementations. Within Altera engineering, this includes Volker Mauer, Martin Langhammer, and Mike Fitton. Within the Altera technical sales organization, people who have been especially helpful to my understanding of some of the relevant DSP applications include Colman Cheung, Ben Esposito, Brian Kurtz, and Mark Santoro.

Within Altera publications, James Adams has been instrumental in getting this project off the ground and working with the publisher.

Finally, the support of my wife, Zaida, and daughter, Ariel, have been most important. This book has been primarily an "evenings and weekends" project, and their patience has been essential.

#### Contents

- 1. Numerical Representation

- 2. Complex Numbers and Exponentials

- 3. Sampling, Aliasing, and Quantization

- 4. Frequency Response

- 5. Finite Impulse Response (FIR) Filters

- 6. Windowing

- 7. Decimation and Interpolation

- 8. Infinite Impulse Response (IIR) Filters

- 9. Complex Modulation and Demodulation

- 10. Discrete and Fast Fourier Transforms (DFT, FFT)

- 11. Numerically Controlled Oscilators

- 12. Digital Up and Down Conversion

- 13. Error Corrective Coding

- 14. CDMA Modulation and Demodulation

- 15. OFDM Modulation and Demodulation

- 16. Discrete Cosine Transform (DCT)

- 17. Video and Image Processing

- 18. Video Compression and Decompression

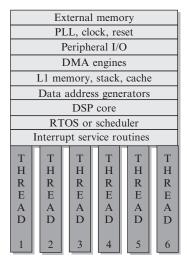

- 19. Implementation Using Digital Signal Processors

- 20. Implementation Using FPGAs

- 21. Design and Debug Methodology Trends

- 22. Future Implementation Trends

Appendix A: Q Format Shift with Fractional Multiplication Appendix B: Evaluation of FIR Design Error Minimization Appendix C: Laplace Transform Appendix D: Z Transform

## Numerical Representation

To process a signal digitally, it must be represented in a digital format. This point may seem obvious, but it turns out that there are a number of different ways to represent numbers, and this representation can greatly affect both the result and the number of circuit resources required to perform a given operation. This chapter is focused more for people who are implementing digital signal processing (DSP) and is not really required to understand DSP fundamental concepts.

Digital electronics operate on bits, of course, which are used to form binary words. The bits can be represented as binary, decimal, octal, hexadecimal, or another form. These binary numbers can be used to represent "real" numbers. There are two basic types of arithmetic used in DSP: floating point and fixed point. Fixed-point numbers have a fixed decimal point as part of the number. Examples are 1234 (the same as 1234.0), 12.34, and 0.1234. This is the type of number we normally use every day. A floating-point number has an exponent. The most common example is scientific notation, used on many calculators. In floating point, 1,200,000 would be expressed as  $1.2 \times 10^6$ , and 0.0000234 would be expressed as  $2.34 \times 10^{-5}$ . Most of our discussion will focus on fixed-point numbers, as they are most commonly found in DSP applications. Once we understand DSP arithmetic issues with fixed-point numbers, then there is short discussion of floating-point numbers.

In DSP, we pretty much exclusively use signed numbers, meaning that there are both positive and negative numbers. This leads to the next point, which is how to represent the negative numbers.

In signed fixed-point arithmetic, the binary number representations include a sign, a radix or decimal point, and the magnitude. The sign indicates whether the number is positive or negative, and the radix (also called decimal) point separates the integer and fractional parts of the number.

The sign is normally determined by the leftmost, or most significant bit (MSB). The convention is that a zero is used for positive and one for negative. There are several formats to represent negative numbers, but the almost universal method is known as 2s complement. This is the method discussed here.

Furthermore, fixed-point numbers are usually represented as either integer or fractional. In integer representation, the decimal point is to the right of the least significant bit (LSB), and there is no fractional part in the number. For an 8-bit number, the range that can be represented is from 128 to +127, with increments of 1.

In fractional representation, the decimal point is often just to the right of the MSB, which is also the sign bit. For an 8-bit number, the range that can be represented is from 1 to +127/128 (almost +1), with increments of 1/128. This may seem a bit strange, but in practice, fractional representation has advantages, as will be explained.

This chapter presents several tables, with each row giving equivalent binary and hexadecimal numbers. The far right column gives the actual value in the chosen representation—for example, 16-bit integer representation. The actual value represented by the hex/binary numbers depends on which representation format is chosen.

#### 1.1 Integer Fixed-Point Representation

The following table provides some examples showing the 2s complement integer fixed-point representation.

| Binary    | Hexadecimal | Actual Decimal Value |

|-----------|-------------|----------------------|

| 0111 1111 | 0x7F        | 127                  |

| 0111 1110 | 0x7E        | 126                  |

| 0000 0010 | 0x02        | 2                    |

| 0000 0001 | 0x01        | 1                    |

| 0000 0000 | 0x00        | 0                    |

| 1111 1111 | 0xFF        | 1                    |

| 1111 1110 | 0xFE        | 2                    |

| 1000 0001 | 0x81        | 127                  |

| 1000 0000 | 0x80        | 128                  |

Table 1.1: 8-Bit integer representation

The 2s complement representation of the negative numbers may seem nonintuitive, but it has several very nice features. There is only one representation of 0 (all 0s), unlike other formats that have a "positive" and "negative" zero. Also, addition and multiplication of positive and negative 2s complement numbers work properly with traditional digital adder and multiplier structures. A 2s complement number range can be extended to the left by simply replicating the MSB (sign bit) as needed, without changing the value.

The way to interpret a 2s complement number is to use the mapping for each bit shown in the following table. A 0 bit in a given location of the binary word means no weight for that bit. A 1 in a given location means to use the weight indicated. Notice the weights double with each bit moving left, and the MSB is the only bit with a negative weight. You should satisfy yourself that all negative numbers will have an MSB of 1, and all positive numbers and zero have an MSB of 0.

| 8-Bit Signed Integer  | MSB            |                |                |                |                |                |                | LSB            |

|-----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Bit weight            | 128            | 64             | 32             | 16             | 8              | 4              | 2              | 1              |

| Weight in powers of 2 | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |

Table 1.2: 2s complement bit weighting with 8 bit words

This can be extended to numbers with larger number of bits. Following is an example with 16 bits. Notice how the numbers represented in a lesser number of bits (e.g., 8 bits) can be easily put into 16-bit representation by simply replicating the MSB of the 8-bit number eight times and tacking onto the left to form a 16-bit number. Similarly, as long as the number represented in the 16-bit representation is small enough to be represented in 8 bits, the leftmost bits can simply be shaved off to move to the 8-bit representation. In both cases, the decimal point stays to the right of the LSB and does not change location. This can be seen easily by comparing, for example, the representation of 2 in the 8-bit representation table and again in the 16-bit representation table.

| Binary              | Hexadecimal | Actual Decimal Value |

|---------------------|-------------|----------------------|

| 0111 1111 1111 1111 | 0×7FFF      | 32,767               |

| 0111 1111 1111 1110 | 0×7FFE      | 32,766               |

| 0000 0000 1000 0000 | 0×0080      | 128                  |

| 0000 0000 0111 1111 | 0×007F      | 127                  |

| 0000 0000 0111 1110 | 0×007E      | 126                  |

| 0000 0000 0000 0010 | 0×0002      | 2                    |

| 0000 0000 0000 0001 | 0×0001      | 1                    |

| 0000 0000 0000 0000 | 0×0000      | 0                    |

| 1111 1111 1111 1111 | 0×FFFF      | 1                    |

| 1111 1111 1111 1110 | 0×FFFE      | 2                    |

| 1111 1111 1000 0001 | 0×FF81      | 127                  |

| 1111 1111 1000 0000 | 0×FF80      | 128                  |

| 1111 1111 0111 1111 | 0×FF80      | 129                  |

| 1000 0000 0000 0001 | 0×FF80      | 32,767               |

| 1000 0000 0000 0000 | 0×FF80      | 32,768               |

Table 1.3: 16-Bit signed integer representation

| Table 1.4: | 2s complement | bit weighting with | 16 bit word |

|------------|---------------|--------------------|-------------|

|------------|---------------|--------------------|-------------|

| MSB             |                 |                 |                 |                 |                 |                |                |                |                |                |                |                |                |                | LSB            |

|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 32,<br>768      | 16,<br>384      | 8192            | 4096            | 2048            | 1024            | 512            | 256            | 128            | 64             | 32             | 16             | 8              | 4              | 2              | 1              |

| 2 <sup>15</sup> | 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 2 <sup>11</sup> | 2 <sup>10</sup> | 2 <sup>9</sup> | 2 <sup>8</sup> | 2 <sup>7</sup> | 2 <sup>6</sup> | 2 <sup>5</sup> | 2 <sup>4</sup> | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 2 <sup>0</sup> |

Now, let's look at some examples of trying to adding combinations of positive and negative 8-bit numbers together using a traditional unsigned digital adder. We throw away the carry bit from the last (MSB) adder stage.

| Case #1: Positive and negative            | number sum                                              |                    |

|-------------------------------------------|---------------------------------------------------------|--------------------|

| +15                                       | 0000 1111                                               | 0x0F               |

| -1                                        | 1111 1111                                               | 0xFF               |

| +14                                       | 0000 1110                                               | 0x0E               |

| Case #2: Positive and negative            | number sum                                              |                    |

| -31                                       | 1110 0001                                               | 0xE1               |

| +16                                       | 0001 0000                                               | 0x80               |

| -15                                       | 1111 0000                                               | 0xF0               |

| Case #3: Two negative number              | rs being summed                                         |                    |

| -31                                       | 1110 0001                                               | 0xE1               |

| -64                                       | 1100 0000                                               | 0xC0               |

| -95                                       | 1010 0001                                               | 0xF0               |

| Case #4: Two positive number              | s being summed; result exceeds range                    |                    |

| +64                                       | 0100 0000                                               | 0x40               |

| +64                                       | 0100 0000                                               | 0x40               |

| +128                                      | 1000 0000**                                             | 0x80**             |

| Notice all the results are correct except | t the last case. The reason is that the result, $\pm 1$ | 28. cannot be repr |

<sup>\*\*</sup>Notice all the results are correct, except the last case. The reason is that the result, +128, cannot be represented in the range of an 8 bit 2s complement number.

Integer representation is often used in many software applications because it is familiar and works well. However, in DSP, integer representation has a major drawback. In DSP, there is a lot of multiplication. When you multiply a bunch of integers together, the results start to grow rapidly. It quickly gets out of hand and exceeds the range of values that can be represented. As we saw previously, 2s complement arithmetic works well, as long as you do not exceed the numerical range. This has led to the use of fractional fixed-point representation.

#### 1.2 Fractional Fixed-Point Representation

The basic idea behind fractional fixed-point representation is all values are in the range from +1 to -1, so if they are multiplied, the result will not exceed this range. Notice that, if you want to convert from integer to 8-bit signed fractional, the actual values are all divided by 128. This maps the integer range of +127 to -128 to almost +1 to -1.

| Binary    | Hexadecimal | Actual Decimal Value |

|-----------|-------------|----------------------|

| 0111 1111 | 0x7F        | 127/128 = 0.99219    |

| 0111 1110 | 0x7E        | 126/128 = 0.98438    |

| 0000 0010 | 0x02        | 2/128 = 0.01563      |

| 0000 0001 | 0x01        | 1/128 = 0.00781      |

| 0000 0000 | 0x00        | 0                    |

| 1111 1111 | 0xFF        | 1/128 = 0.00781      |

| 1111 1110 | 0xFE        | 2/128 = 0.01563      |

| 1000 0001 | 0x81        | 127/128 = 0.99219    |

| 1000 0000 | 0x80        | 1.00                 |

Table 1.5: 8-Bit fractional representation

Table 1.6: 2s complement weighting for 8 bit fractional word

| 8-Bit Signed Fractional | MSB            |                 |                 |          |          |          |                 | LSB             |

|-------------------------|----------------|-----------------|-----------------|----------|----------|----------|-----------------|-----------------|

| Weight                  | 1              | 1/2             | 1/4             | 1/8      | 1/16     | 1/32     | 1/64            | 1/128           |

| Weight in powers of 2   | 2 <sup>0</sup> | 2 <sup>-1</sup> | 2 <sup>-2</sup> | $2^{-3}$ | $2^{-4}$ | $2^{-5}$ | 2 <sup>-6</sup> | 2 <sup>-7</sup> |

Table 1.7: 16-Bit signed fractional representation

| Binary              | Hexadecimal | Actual Decimal Value |

|---------------------|-------------|----------------------|

| 0111 1111 1111 1111 | 0x7FFF      | 32,767/32,768        |

| 0111 1111 1111 1110 | 0x7FFE      | 32,766/32,768        |

| 0000 0000 1000 0000 | 0x0080      | 128/32,768           |

| 0000 0000 0111 1111 | 0x007F      | 127/32,768           |

| 0000 0000 0111 1110 | 0x007E      | 126/32,768           |

| 0000 0000 0000 0010 | 0x0002      | 2/32,768             |

| 0000 0000 0000 0001 | 0x0001      | 1/32,768             |

| 0000 0000 0000 0000 | 0x0000      | 0                    |

| 1111 1111 1111 1111 | 0xFFFF      | 1/32,768             |

| 1111 1111 1111 1110 | 0xFFFE      | 2/32,768             |

| 1111 1111 1000 0001 | 0xFF81      | 127/32,768           |

| 1111 1111 1000 0000 | 0xFF80      | 128/32,768           |

| 1111 1111 0111 1111 | 0xFF7F      | 129/32,768           |

| 1000 0000 0000 0001 | 0x8001      | 32,767/32,768        |

| 1000 0000 0000 0000 | 0x8000      | 1                    |

| Table 1.8: | 2s com | plement | weighting | for | 16 | bit | fractional | word |

|------------|--------|---------|-----------|-----|----|-----|------------|------|

|            |        |         |           |     |    |     |            |      |

| MSB            |     |     |     |          |          |          |           |           |           |            |            |            |            |              | LSB          |

|----------------|-----|-----|-----|----------|----------|----------|-----------|-----------|-----------|------------|------------|------------|------------|--------------|--------------|

| 1              | 1/2 | 1/4 | 1/8 | 1/<br>16 | 1/<br>32 | 1/<br>64 | 1/<br>128 | 1/<br>256 | 1/<br>512 | 1/<br>1024 | 1/<br>2048 | 1/<br>4096 | 1/<br>8192 | 1/16,<br>384 | 1/32,<br>768 |

| 2 <sup>0</sup> | 2 1 | 2 2 | 2 3 | 2 4      | 2 5      | 2 6      | 2 7       | 2 8       | 2 9       | 2 10       | 2 11       | 2 12       | 2 13       | 2 14         | 2 15         |

Fractional fixed point is often expressed in Q format. The representation shown above is Q15, which means that there are 15 bits to the right of the radix or decimal point. It might also be called Q1.15, meaning that there are 15 bits to right of the decimal point and one bit to the left.

The key property of fractional representation is that the numbers grow smaller, rather than larger, during multiplication. And in DSP, we commonly sum the results of many multiplication operations. In integer math, the results of multiplication can grow large quickly (see the following example). And when we sum many such results, the final sum can be very large, easily exceeding the ability to represent the number in a fixed-point integer format.

As an analogy, think about trying to display an analog signal on an oscilloscope. You need to select a voltage range (volts/division) in which the signal amplitude does not exceed the upper and lower range of the display. At the same time, you want the signal to occupy a reasonable part of the screen, so the detail of the signal is visible. If the signal amplitude occupies only 1/10 of a division, for example, it is difficult to see the signal.

To illustrate this situation, imagine using a 16-bit fixed point, and the signal has a value of 0.75 decimal or 24,676 in integer (which is 75% of full scale), and is multiplied by a coefficient of value 0.50 decimal or 16,384 integer (which is 50% of full scale).

| 0.75          | 24,576      |

|---------------|-------------|

| $\times$ 0.50 | × 16,384    |

| 0.375         | 402,653,184 |

Now the larger integer number can be shifted right after every such operation to scale the signal within a range that it can be represented, but most DSP designers prefer to represent numbers as fractional because it is a lot easier to keep track of the decimal point.

Now consider multiplication again. If two 16-bit numbers are multiplied, the result is a 32-bit number. As it turns out, if the two numbers being multiplied are Q15, you might expect the result in the 32-bit register to be a Q31 number (MSB to the left of the decimal point, all other bits to the right). Actually, the result is in Q30 format; the decimal point has shifted down to the right. Most DSP processors will automatically left shift the multiplier output to compensate for this when operating in fractional arithmetic mode. In Field Programmable Gate Array (FPGA) or hardware design, the designer may have to take this into account when connecting data buses between different blocks. Appendix A explains the need for this extra left shift in detail, as it will be important for those implementing fractional arithmetic on FPGAs or DSPs.

| 0×4000                 | value = $\frac{1}{2}$ in Q15 |

|------------------------|------------------------------|

| $\times 0 \times 2000$ | value = $\frac{1}{4}$ in Q15 |

| 0×0800 0000            | value = $1/16$ in Q31        |

After left shifting by one, we get

$0 \times 1000\ 0000$  value = 1/8 in Q31 the correct result!

If we use only the top 16-bit word from multiplier output, after the left shift, we get

$0 \times 1000$  value = 1/8 in Q15 again, the correct result!

#### 1.3 Floating-Point Representation

Many of the complications encountered using the preceding methods can be avoided by using floating-point format. Floating-point format is basically like scientific notation on your calculator. Because of this, a floating-point number can have a much greater dynamic range than a fixed-point number with an equivalent number of bits. Dynamic range means the ability to represent very small numbers to very large numbers.

The floating-point number has both a mantissa (which includes sign) and an exponent. The mantissa is the value in the main field of your calculator, and the exponent is off to the side, usually as a superscript. Each is expressed as a fixed-point number (meaning the decimal point is fixed). The mantissa is usually in signed fractional format, and the exponent in signed integer format. The size of the mantissa and exponent in number of bits will vary depending on which floating-point format is used.

The following table shows two common 32-bit formats: "two word" and IEEE 754.

| Floating-Point Formats | ng-Point Formats No. of Mantissa Bits                                  |                                        |

|------------------------|------------------------------------------------------------------------|----------------------------------------|

| "two word"             | 16, in signed Q15                                                      | 16, signed integer                     |

| IEEE STD 754           | 23, in unsigned Q15, plus 1 bit to determine sign (not 2s complement!) | 8, unsigned integer,<br>biased by +127 |

Table 1.9: Floating point format summary

To convert a fixed-point number in floating-point representation, we shift the fixed number left until there are no redundant sign bits. This process is called *normalization*. The number of these shifts determines the exponent value.

The drawback of floating-point calculations is the resources required. When adding or subtracting two floating-point numbers, we must first adjust the number with smaller absolute value so that its exponent is equal to the number with larger absolute value; then we can add

the two mantissas. If the mantissa result requires a left or right shift to represent, the exponent is adjusted to account for this shift. When multiplying two floating-point numbers, we multiply the mantissas and then sum the exponents. Again, if the mantissa result requires a left or right shift to represent, the new exponent must be adjusted to account for this shift. All of this requires considerably more logic than fixed-point calculations and often must run at much lower speed (although recent advances in FPGA floating-point implementation may significantly narrow this gap). For this reason, most DSP algorithms use fixed-point arithmetic, despite the onus on the designer to keep track of where the decimal point is and ensure that the dynamic range of the signal never exceeds the fixed-point representation or else becomes so small that quantization error becomes insignificant. We will see more on quantization error in a later chapter.

If you are interested in more information on floating-point arithmetic, there are many texts that go into this topic in detail, or you can consult the IEEE STD-754 document.

### **Complex Numbers and Exponentials**

Complex numbers are among those things many of us were taught a long time ago and have long since forgotten. Unfortunately, they are important in digital communications and DSP, so we need to resurrect them.

What we were taught—and some of us vaguely remember—is that a complex number has a "real" and an "imaginary" part, and the imaginary part is the square root of a negative number, which is really a nonexistent number. This explanation right away sounds fishy, and while it's technically true, there is a much more intuitive way of looking at it.

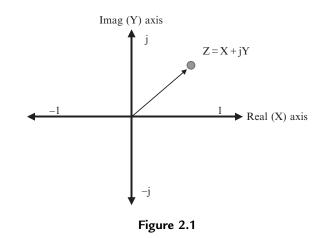

The whole reason for complex numbers is that we are going to need a two-dimensional number plane to understand DSP. The traditional number line extends from plus infinity to minus infinity, along a single line. To represent many of the concepts in DSP, we need two dimensions. This requires two orthogonal axes, like a North–South line and an East–West line. For the arithmetic to work out, one line, usually depicted as the horizontal line, is the real number line. The other vertical line is the imaginary line. All imaginary numbers are prefaced by "j," which is defined as the square root of –1. Don't get confused by this imaginary number stuff, but rather view "j" as an arbitrary construct we will use to differentiate the horizontal axis (normal) numbers from those on the vertical axis. This is the essence of this whole chapter.

As depicted in Figure 2.1, any complex number Z has a real and an imaginary part, and is expressed as  $X + j \cdot Y$  or just X + jY. The value of X and Y for any point is determined by the distance one must travel in the direction of each axis to arrive at the point. It can also be visualized as a point on the complex number plane, or as a vector originating at the origin and terminating at the point. We need to be able to do arithmetic with complex numbers. There has to be a way to keep track of the vertical and horizontal components. That's where the "j" comes in (in some texts, "i" is used instead).

#### 2.1 Complex Addition and Subtraction

Adding and subtracting are simple: just add and subtract the vertical and horizontal components separately. The "j" helps us keep from mixing the vertical and horizontal components. For example,

$$(3+j4)$$

$(1 j6) = 2+j10$

Digital Signal Processing 101. DOI: 10.1016/B978-1-85617-921-8.00006-7

Scaling a complex number is simply scaling each component:

$$4 \cdot (3 + j4) = 12 + j16$$

#### 2.2 Complex Multiplication

Multiplication gets a little trickier and is harder to visualize graphically. Here is the way the mechanics of it work:

$$(A + jB) \cdot (C + jD) = A \cdot C + jB \cdot C + A \cdot jD + jB \cdot jD = AC + jBC + jAD + j^2BD$$

Now remember that  $j^2$  is, by definition, equal to -1. After collecting terms, we get

$$AC + jBC + jAD + j^{2}BD = AC + jBC + jAD$$

$BD = (AC BD) + j(BC + AD)$

The result is another complex number, with AC - BD being the real part and BC + AD being the imaginary part (remember, *imaginary* just means the vertical axis, while *real* is the horizontal axis). This result is just another point on the complex plane.

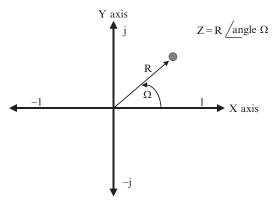

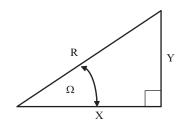

The mechanics of this arithmetic may be simple, but we need to be able to visualize what is really happening. To do this, we need to introduce polar (R,  $\Omega$ ) representation. Until now, we have been using Cartesian (X, Y) coordinates, which means each location on the complex number plane is specified by the distance along each of the two axes (like longitude and latitude on the earth's surface). Polar representation replaces these two parameters, which can specify any point on the complex plane, with another set of two parameters, which also can specify any point on the complex plane. The two new parameters are the magnitude and angle. The *magnitude* is simply the length of the line or vector from the origin to the point. The *angle* is defined as the angle of this line starting at the positive X axis and arcing counterclockwise.

This relationship is shown in Figure 2.2, where the same point Z = X + jY is identified by having radius R (length of the vector from origin to the point) with angle  $\Omega$  specified counterclockwise from the positive real axis.

Figure 2.2

Any point Z on the graph may be specified as X + jY or R with angle  $\Omega$ .

To understand the relationships between these, we need to go back to basic high school math. Consider the right triangle formed in Figure 2.3, with sides X, Y, R, and angle  $\Omega$ .

Figure 2.3

Remember the Pythagorean theorem? For any right triangle,  $X^2 + Y^2 = R^2$ .

Also, remember that sine is defined as the length of the opposite side divided by the hypotenuse, and cosine is defined as the length of the adjacent side divided by the hypotenuse (but it must be a right triangle). Tangent is defined as the opposite over the adjacent side. So we get the following relationships, which can be used to convert between Cartesian (X,Y) and polar (R,  $\Omega$ ).

#### 2.2.1 Polar Representation

$$\begin{array}{lll} \sin(\Omega) = (Y/R) & \Rightarrow & Y = R \cdot \sin(\Omega) \\ \cos(\Omega) = (X/R) & \Rightarrow & X = R \cdot \cos(\Omega) \\ X^2 + Y^2 = R^2 & \Rightarrow & R = \operatorname{sqrt} (X^2 + Y^2) \\ \tan(\Omega) = (X/Y) & \Rightarrow & \Omega = \arctan(X/Y) \end{array}$$

The reason for this little foray into polar representation is that multiplication (and division) of complex numbers is very easy in polar form, and that angles in the complex plane can be easily visualized in polar form.

#### 2.2.2 Complex Multiplication Using Polar Representation

We will define two points,  $Z_1$  and  $Z_2$ :

$$\begin{aligned} &Z_1 = R_1 \text{ angle } (\Omega_1) & Z_2 = R_2 \text{ angle } (\Omega_2) \\ &Z_1 \cdot Z_2 = (R_1 \cdot R_2) \text{ angle } (\Omega_1 + \Omega_2) \end{aligned}$$

This means that with any two complex numbers, the magnitude, or distance from the origin to the radius, gets multiplied together to form the new magnitude. This makes sense intuitively. The angles of the two complex numbers get added together to form the new angle. Not so intuitive, so let's try a few examples to get the hang of it.

Let's use real numbers to start; a real number is just a complex number with the "j" part equal to zero. Real numbers are "simplified" versions of complex numbers, so any arithmetic rules on a complex number had better work with the real numbers.

Z = R angle ( $\Omega$ ) for real numbers, the angle must be equal to  $0^{\circ}$

Then  $X = R \cdot cos(0)$  or X = R and  $Y = R \cdot sin(0)$  or Y = 0. This is what we expect: the Y portion must be zero for the number to lie on the X (real number) axis.

Now consider two complex numbers, both with angle zero:

$\begin{array}{l} Z_1 = R_1 \text{ angle } (0), Z_2 = R_2 \text{ angle } (0) \text{ with the product} \\ Z_1 \cdot Z_2 = R_1 \cdot R_2 \text{ angle } (0+0) = R_1 \cdot R_2 \end{array} ( \text{reverts to traditional multiplication} ) \end{array}$

Now consider another set of complex numbers, both with angles of 180°:

$$Z_1 = R_1$$

angle (180),  $Z_2 = R_2$  angle (180)

From the relation above,  $Y = R \cdot \sin(\Omega)$ ,  $X = R \cdot \cos(\Omega)$ . With angles of 180°, Y = 0, X = -R, meaning the point Z lies on the negative part of the real axis. Z is

simply a negative real number. If we multiply two real negative numbers, we know that we should get a real positive number. Let's check using complex multiplication:

$$Z_1 \cdot Z_2 = R_1 \cdot R_2$$

angle  $(180 + 180) = R_1 \cdot R_2$  angle  $(360)$ .

The angle  $360^{\circ}$  is all the way around the circle and equal to  $0^{\circ}$ :

$$Z_1 \cdot Z_2 = R_1 \cdot R_2$$

angle (360) =  $R_1 \cdot R_2$  angle (0) =  $R_1 \cdot R_2 = X_1 \cdot X_2$

The result is a real positive number.

There is another point to all these exercises, which is to explain why we chose something strange like j equals the square root of -1 to designate the vertical axis in the complex number plane. Be patient; we're almost there.

There are four "special" angles: 0°, 90°, 180°, 270°. Notice that

Z = R angle (0) = X degrees is a positive real number on a positive real axis. Z = R angle (90) = Y degrees is a positive imaginary number on a positive imaginary axis.

Z = R angle (180) = -X degrees is a negative real number on a negative real axis.

Z = R angle (270) = -Y degrees is a negative imaginary number on a negative imaginary axis.

If we add 360° to any complex number, it wraps all the way around the circle. Or we can have a negative angle, which means just going backward (clockwise) around the circle:

Z = R angle (0) = R angle (360) = R angle (720)... Z = R angle (120) = R angle (480) = R angle (840)... Z = R angle (90) = R angle (-270) = R angle (-630)...Z = R angle (-53) = R angle (307) = R angle (667)...

We now know when multiplying two complex numbers, the magnitudes R are multiplied and the angles  $\Omega$  are summed. Now let's consider a few sample cases to illustrate how this imaginary "j" operator helps us.

Imagine two complex numbers with only an imaginary component. They are both located on the positive imaginary axis:

$$\begin{aligned} &Z_1=jY_1, Z_2=jY_2 \quad (\text{real parts } X_1=X_2=0) \\ &Z_1\cdot Z_2=jY_1\cdot jY_2=j\cdot j\cdot Y_1\cdot Y_2 \end{aligned}$$

Recall, we defined j = sqrt(-1), so  $j^2 = -1$

$Z_1 \cdot Z_2 = (Y_1 \cdot Y_2)$ , a negative real number

Or equivalently,

$$\begin{array}{ll} Z_1 = R_1 \text{ angle } (90), \ Z_2 = R_2 \text{ angle } (90) \\ Z_1 \cdot Z_2 = R_1 \cdot R_1 \text{ angle } (180) = & (R_1 \cdot R_2) = & (Y_1 \cdot Y_2) \text{ since } X_1 = X_2 = 0 \end{array}$$

You can experiment with other combinations, but what you will find is that the arithmetic of adding angles around the circle when multiplying complex numbers works out perfectly when we designate the positive imaginary axis with j and the negative imaginary axis with -j.

By visualizing this business of going around the circle, you can see by inspection that

• Multiply two positive real numbers, both angles = 0, the result has an angle of zero:

$$3 \cdot 5 = 15$$

Multiply two negative real numbers, both angles = 180 (or -180), the result has an angle of zero (or 360):

$$3 \cdot 5 = 15$$

• Multiply a positive real number (angle 0) with a negative real number (angle 180), the result has an angle of 180, a negative real number:

$$3 \cdot 5 = 15$$

• Multiply a positive real number (angle 0) with a positive imaginary number (angle 90), the result has an angle of 90, an imaginary number:

$$j3 \cdot 5 = j15$$

• Multiply a positive imaginary number (angle 0) with a positive imaginary number (angle 90), the result has an angle of 180, a negative real number:

$$j3 \cdot j5 = j^2 \cdot 15 = 15$$

• Multiply a negative imaginary number (angle 90) with a negative imaginary number (angle 90), the result has an angle of 180, a negative real number:

$$j3 \cdot j5 = (j) \cdot (j) \cdot 15 = ((15)) = 15$$

• Multiply a positive imaginary number (angle 90) with a negative imaginary number (angle –90), the result has an angle of 0, a positive real number:

$$j3 \cdot j5 = j \cdot (j) \cdot 15 = ((15)) = 15$$

#### www.newnespress.com

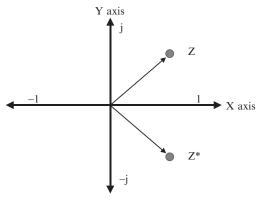

#### 2.3 Complex Conjugate

The last example illustrates a special case. Every number Z = R angle ( $\Omega$ ) has what is called a *complex conjugate*,  $Z^* = R$  angle ( $-\Omega$ ). In the earlier example,  $\Omega = 90$ , but  $\Omega$  can be any angle. The \* symbol is the complex conjugate symbol, and means to take the point Z and mirror it across the X axis as shown in Figure 2.4.

Figure 2.4

So Z = X + jY has the conjugate  $Z^* = X - jY$ . We just negate or reverse the sign of the imaginary part of a number to get its conjugate, or if in polar form, just negate the sign of the angle:

$$Z = R$$

angle ( $\Omega$ ),  $Z^* = R$  angle ( $\Omega$ )

A special property of the complex conjugate is that for any complex number

$$Z \cdot Z^* = R$$

angle  $(\Omega) \cdot R$  angle  $(\Omega) = R^2$  angle $(0)$ .

In other words, when you multiply a number by its conjugate, the product is a real number, equal to the magnitude squared. This point will become important in digital signal processing because it can be used to compute the power of a complex signal.

To summarize, we have tried to show that the imaginary numbers that are used to form things called *complex* numbers are really not so complex, and *imaginary* is really a very misleading description. What we have really been trying to do is to create a twodimensional number plane and define a set of expanded arithmetic rules to manipulate the numbers in it. Now we are ready to move onto the next topic, the complex exponential.

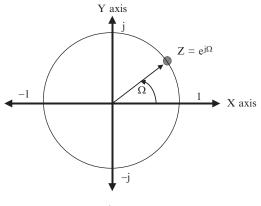

#### 2.4 The Complex Exponential

The complex exponential has an intimidating sound to it, but in reality, it is very simple to visualize. It is simply the unit circle (radius = 1) on the complex number plane (see Figure 2.5).

Figure 2.5

Any point on the unit circle can be represented by "e" or raised to the power  $(j \cdot angle)$  or also expressed as  $e^{j\Omega}$ , which is called a complex exponential function. A few examples should help.

Let the angle  $\Omega = 0^{\circ}$ . Anything raised to the power 0 is equal to 1. This checks out, since this is the point 1 on the positive real axis.

Let angle  $\Omega = 90^{\circ}$ . The complex exponential is  $e^{j90}$ . This is the point j on the positive imaginary axis. We need a way to evaluate the complex exponential to show this point. This leads to the Euler equation. This equation can easily be derived using Taylor series expansion for exponentials, but we've promised to minimize the math. The result is

$$e^{j\Omega} = \cos(\Omega) + j\sin(\Omega)$$

Let's try exp(j90) again. Using the Euler equation, we get

$$e^{j90} = \cos(90) + j\sin(90) = 0 + j \cdot 1 = j$$

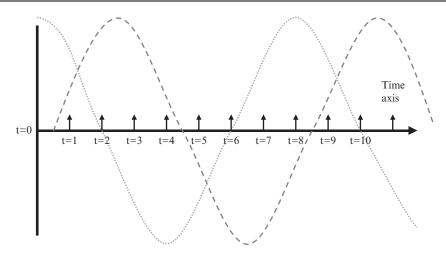

Imagine the point  $Z = e^{j\Omega}$  with the angle  $\Omega$  starting at 0° and gradually increasing to 360°. This will start at the point +1 on the real axis and move counterclockwise around the circle until it ends up where it started, at 1 again. If the angle starts at 0 and gradually decreases until it reaches -360, the point will do exactly the same thing, except rotate in a clockwise fashion.

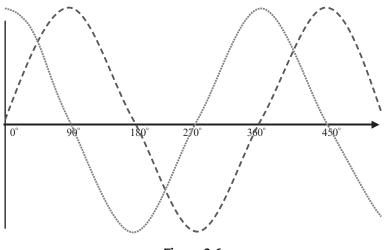

Now we know from the Euler equation that the complex exponential has a real and an imaginary component. Try to imagine the movement of the point on the unit circle as reflected on the real axis (imagine a second point, allowed to move only on the real axis, trying to follow the first point as it moves about the circle). The movement of the second point on the real axis will equal to  $\cos(\Omega)$ . So if we continually rotate in either direction about the unit circle, the real component will move back and forth between +1 and -1 using the motion of the cosine function. Similarly, the movement of the point on the unit circle as reflected on the imaginary axis will be similar, except instead of starting at a value of +1, it will start with a value of 0. The pattern of motion will lag by 90°. The imaginary axis movement is equal to  $j \cdot \sin(\Omega)$ , and the imaginary component will move back and forth between j and -j using the sine function.

This scenario is shown in Figure 2.6, where the dashed line represents the imaginary axis movement of  $j \cdot \sin(\Omega)$  and the dotted line represents the real axis movement of  $\cos(\Omega)$ .

Figure 2.6

$\begin{aligned} X &= \cos{(\Omega)} & (real axis movement) \\ Y &= \sin{(\Omega)} & (imaginary axis movement) \end{aligned}$

This gives us a better way to express a complex number in polar coordinates:

Recall Z = X + jY = R angle ( $\Omega$ )

As we saw before,

$X = \operatorname{Rcos} (\Omega)$  $Y = \operatorname{Rsin} (\Omega)$

So we can see that angle  $(\Omega)$  has the same meaning as  $\exp(j\Omega)$ . Also, for the unit circle, R = 1 by definition. So our new way to express a number in polar form using the complex exponential is

Z = R angle  $(\Omega) = R e^{j\Omega}$  (any point in a complex plane)  $Z = angle (\Omega) = e^{j\Omega}$  (for R = 1, any point on the unit circle)

This is the way you will often see these expressions in the textbooks and industry literature.

#### 2.5 Measuring Angles in Radians

The last curve ball in this chapter involves measuring angles in radians. You will have to get accustomed to this format because you will see it everywhere in DSP. In our discussion, to make things more familiar, we will start measuring angles in degrees, where  $360^{\circ}$  describes a full circle. More commonly, the angle measurement in radians is based on  $\pi$ , which is a number defined to have a value of about 3.141592 (it actually is an irrational number, with an infinite number of digits, like 1/3 = 0.3333...). It takes exactly  $2\pi$  radians to describe a full circle (see Table 2.1).

| Angle in Degrees | Angle in Radians    |

|------------------|---------------------|

| 0                | 0 π                 |

| 45               | $\pi/4$             |

| 90               | π/2                 |

| 180 = 180        | $\pi = \pi$         |

| 270 = 90         | $(3/2) \pi = \pi/2$ |

| 360 = 0          | $2\pi=0\pi$         |

| 360 = 0          | $2\pi = 0\pi$       |

| 540 = 180        | $3\pi = \pi$        |

| 540 = 180 = 180  | $3\pi = \pi = \pi$  |

Table 2.1: Equivalence between degrees and radians

Just as angle measurements are periodic in  $360^{\circ}$ , they are also periodic in  $2\pi$  radians. Using  $\pi$  is really no different than getting used to meters rather than using feet for measuring distances (or the reverse if you didn't grow up in the United States). We are going to see this same concept later in sampling theory, where everything tends to wrap around, or behave periodically. We can visualize this concept as traveling either clockwise (negative rotation) or counterclockwise (positive rotation) around the circle.

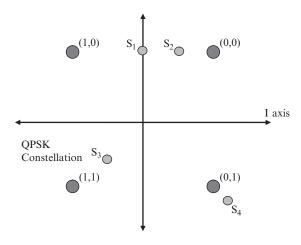

There is one more DSP convention to be aware of. The real component (we used X in the preceding discussion) is usually called the "I," or in-phase component, and the imaginary component (we used Y in the preceding discussion) is usually referred to as the "Q," or quadrature phase component. In many DSP algorithms, the digital signal processing must be performed simultaneously on both I and Q data streams, which we now know simply represent the signal's movement, over time, within the two dimensions of our complex number plane.

## Sampling, Aliasing, and Quantization

Now that we have the basic background material covered, let's start talking about DSP. The starting point we need to understand is sampling and its effect on the signal of interest. To take an analog signal and convert it to a digital signal, we need to sample the signal using a device called an analog-to-digital converter (ADC). The ADC measures the signal at rapid intervals, and these measurements are called samples. It outputs a digital signal proportional to the amplitude of the analog signal at that instant. This scenario can be compared to looking at an object with only a strobe light for illumination. You can see the object only when the strobe light flashes. If the object is not moving, then everything looks pretty much the same, as if we had used a normal, continuous light source. Things get interesting when we look at a moving object with the strobe light. If the object is moving rapidly, then the appearance of the motion can be quite different from that viewed under normal light. We can also see strange effects even if the object is moving fairly slowly, and we reduce the rate of the strobe light enough. Intuitively, we can see that what is important is the rate of the strobe light compared to the rate of movement of the illuminated object. As long as the light is strobing fast compared to the movement of the object, the movement of the object looks very fluid and normal. When the light is strobing slowly compared to the rate of object movement, the movement of the object looks funny, often like slow motion, because we can see the object is moving, but we miss the sense of continuous, fluid movement.

Let's examine one more example many of us experienced as children. Imagine trying to make your own animated movie and sketching a character on index cards. We want to depict this character moving, perhaps jumping and falling. We might sketch 20 or 40 cards, each showing the same character in sequential stages of this motion, with just small movement changes from one card to the next. When we are finished, we can show it to our friends by holding one edge of the deck of index cards and flipping through it quickly by thumbing the other edge. We see our character in this continuous motion of jumping and falling by flipping through the deck of index cards in a second or two.

Actually, whenever we watch TV, this same thing is occurring. But the TV is updating the screen at about 60 times per second, which is rapid enough that we don't notice the separate frames, and we think that we are seeing continuous motion.

So it makes sense that if we sample a signal very fast compared to how rapidly the signal is changing, we get a pretty accurate sampled representation of the signal, but if we sample too slow, we see a distorted version of the signal.

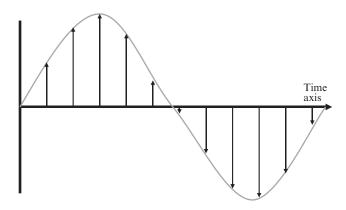

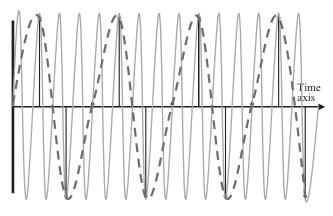

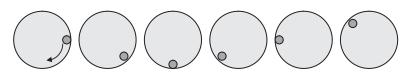

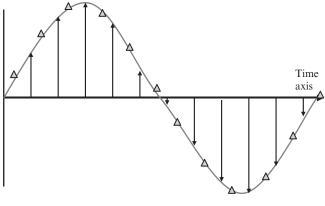

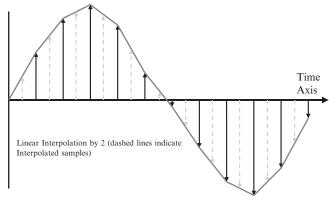

Digital Signal Processing 101. DOI: 10.1016/B978-1-85617-921-8.00007-9 © 2010 Elsevier Inc. All rights reserved. The graphs in Figures 3.1 and 3.2 show two different sinusoidal signals being sampled. The slower moving signal (lower frequency) in Figure 3.1 can be represented accurately with the indicated sample rate, but the faster moving signal (higher frequency) in Figure 3.2 is not accurately represented by our sample rate. In fact, it actually appears to be a slow-moving (low frequency) signal, as indicated by the dashed line. This shows the importance of sampling fast enough for a given frequency signal.

**Figure 3.1:** Sampling a low-frequency signal (arrows indicate sample instants).

**Figure 3.2:** Sampling a high-frequency signal (same sample instants).

The dashed line in Figure 3.2 shows how the sampled signal will appear if we connect the sample dots and smooth out the signal. Notice that since the actual (solid line) signal is changing so rapidly between sampling instants, this movement is not apparent in the sampled version of the signal. The sampled version actually appears to be a lower frequency signal than the actual signal. This effect is known as aliasing.

We need a way to quantify how fast we must sample to accurately represent a given signal. We also need to better understand exactly what is happening when aliasing occurs. The idea may seem strange, but in some instances aliasing can be useful.

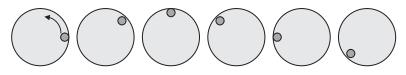

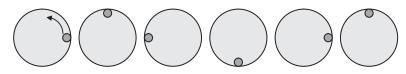

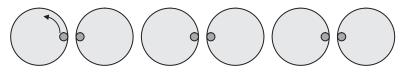

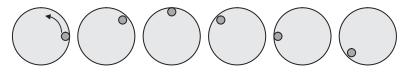

Let's go back to the analogy of the strobe light and try another thought experiment. Imagine a spinning wheel with a single dot near the edge. Let's set the strobe light to flash every 1/8 of a second, or 8 times per second. Figures 3.3 through 3.10 show what we see over six flashes, depending on how fast the wheel is rotating. Time increments from left to right in all figures.

Wheel rotating counterclockwise once per second, or 1 Hz

**Figure 3.3:** The dot moves 1/8 of a revolution, or  $\pi/4$  radians with each strobe flash.

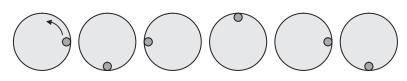

Wheel rotating counterclockwise twice per second, or 2 Hz

Figure 3.4:

Now the dot moves twice as fast,  $\frac{1}{4}$  of a revolution, or  $\pi/2$  radians with each strobe flash.

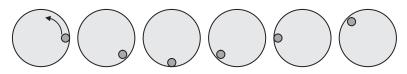

Wheel rotating counterclockwise 4 times per second, or 4 Hz

#### Figure 3.5:

The dot moves  $\frac{1}{2}$  of a revolution, or  $\pi$  radians with each strobe flash. It appears to alternate on each side of the circle with each flash. Can you be sure which direction the wheel is rotating?

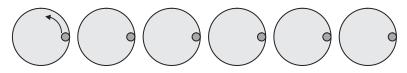

Wheel rotating counterclockwise 6 times per second, or 6 Hz

Figure 3.6:

The dot moves counterclockwise 3/4 of a revolution, or  $3/2\pi$  radians with each strobe flash. But it appears to be moving backward (clockwise).

Wheel rotating counterclockwise 7 times per second, or 7 Hz

Figure 3.7:

The dot moves almost a complete revolution counterclockwise,  $7/4\pi$  radians with each strobe flash. Now it definitely appears to be moving backward (clockwise).

Wheel rotating counterclockwise 8 times per second, or 8 Hz

Figure 3.8:

It looks as though the dot stopped moving! Here, the dot completes exactly one revolution  $(2\pi \text{ radians})$  every strobe interval. You can't tell whether the wheel is moving at all, spinning forward or backward. In fact, could the wheel be rotating twice per strobe interval  $(4\pi \text{ radians})$ ?

Wheel rotating counterclockwise 9 times per second, or 9 Hz

#### Figure 3.9:

The image sure looks the same as when the wheel was rotating once per second, or 1 Hz. In fact, the wheel is moving  $9/4\pi$  radians with each strobe flash.

Wheel rotating backward (clockwise) once per second, or -1 Hz

#### Figure 3.10:

Now we stopped the wheel and started rotating backward at  $-\pi/4$  radians with each strobe flash. Notice that this appears exactly the same as when we were rotating forward at  $7/4\pi$  radians with each strobe flash.

Doesn't all this look familiar from the preceding chapter? The positive rotation is wrapping around and appears like a negative rotation as the wheel speed increases. And the rotation perception appears periodic in  $2\pi$  radians per strobe, just like the angle measurements.

The reality is that once we sample a signal (this is what we are doing by flashing the strobe light), we cannot be sure what has happened in between flashes. Our natural instinct is to assume that the signal (or dot in our example) took the shortest path from where it appears in one flash and then in the subsequent flash. But as we can see in the preceding figures, this assumption can be misleading. The dot could be moving around the circle in the opposite direction (taking the longer path) to get to the point where we see it on the next flash. Or imagine that the wheel is rotating in the assumed direction, but it rotates one full revolution plus "a little bit extra" every flash (the 9 Hz diagram). What we see is only the "a little bit extra" on every flash. For that matter, the wheel could go around 10 times plus the same "a little bit extra," and we could not tell the difference.

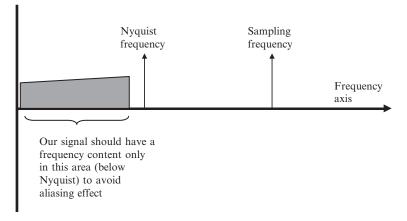

#### 3.1 Nyquist Sampling Rule

To prevent this confusion, we have to come up with a sampling rule, or convention. What we are going to agree is that we will always sample (or strobe) at least twice as fast as the frequency of the signal we are interested in. And in reality, we need to have some margin, so we had better make sure we are sampling *more* than twice as fast as our signal. Going back to the preceding example, at what point do things start to get fishy?

Consider what happens when we start the wheel moving slowly in a counterclockwise direction. Everything looks fine until we reach a rotational speed of 4 Hz. At this point the dot will appear to be alternating on either side of the circle with each strobe flash. Once we have reached this point, we can no longer tell which direction the wheel is rotating; it will look the same rotating both directions. This is the critical point, where we are sampling at

exactly twice as fast as the signal. The sampling speed is the frequency of the strobe light (this would be analogous to the ADC sample frequency), eight times per second, or 8 Hz. The rotational speed of the wheel (our signal) is 4 Hz.

If we spin the wheel any faster, it appears as though it begins to move backward (clockwise), and by the time we reach a rotational speed of 8 Hz, it appears to stop altogether. Spinning still faster will appear as though the wheel moves forward again, until it again appears to start going backward and the cycle repeats.

To summarize, whenever you have a sampled signal, you cannot really be sure of its frequency. But if you assume that the rule was followed—that the signal was sampled at more than twice the frequency of the signal itself—then the sampled signal will really represent the same frequency as the actual signal prior to sampling. The critical frequency that the signal must not ever exceed, which is one half of the sampling frequency, is called the *Nyquist* frequency.

If we follow this rule, then we can avoid the aliasing phenomenon we demonstrated with the moving wheel example earlier. Normally, the ADC converter frequency is selected to be high enough to sample the signal on which we want to perform digital signal processing. To make sure that unwanted signals above the Nyquist frequency do not enter the ADC and cause aliasing, the desired signal in usually passed through an analog low-pass filter, which attenuates any unwanted high-frequency content signals, just prior to the ADC.

A common example is the telephone system. Our voices are assumed to have a maximum frequency of about 3600 Hz. At the microphone, our voice is filtered by an analog filter to eliminate, or at least substantially reduce, any frequencies above 3600 Hz. Then the microphone signal is sampled at 8000 Hz, or 8 kHz. All subsequent digital signal processing occurs on this 8 kSPS (kilo-samples per second) signal. That is why if you hear music in the background while on the telephone, the music will sound flat or distorted. Our ears can detect up to about 15 kHz frequencies, and music generally has frequency content exceeding 3600 Hz. But little of this higher frequency content will be passed through the telephone system.

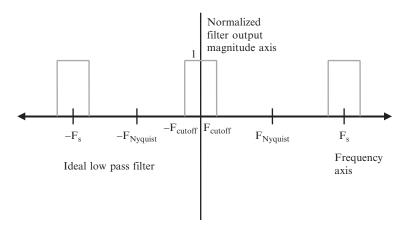

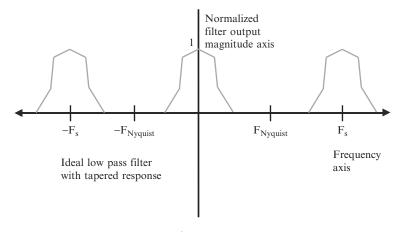

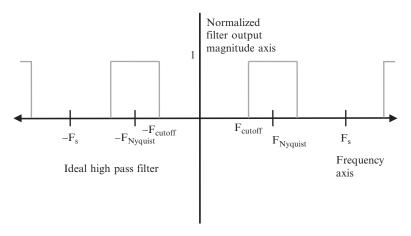

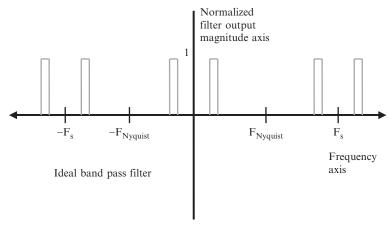

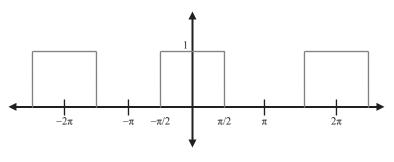

In the next chapter, we will start representing our signals and sampling in the frequency (or spectral) domain. This means that when we plot the signal spectrum, the X axis will represent increasing frequency (see Figure 3.11).

So far, we have covered the most important effects of sampling, but there remains one last issue related to sampling: quantization. We saw earlier how a digital signal is represented numerically and how we must be sure that the numbers representing the sampled signal do not exceed the range of our binary or hexadecimal number range.

Figure 3.11

#### 3.2 Quantization

What happens if the signals are very small? Remember in our discussion of signed fractional 8-bit fixed-point numbers, the range of values we could represent was from 1 to +1 (well, almost +1). The step size was 1/128, which works out to 0.0078125. Let's say the signal has an actual value of 0.5030 at the instant in time we sample it, using an 8-bit ADC. How closely can the ADC represent this value? Let's compare this to a signal that is 1/10 the level of our first sample, or 0.0503. And again, consider a signal with a value 1/10 the level of the second sample, at 0.00503. The following table shows the possible outputs from an 8-bit ADC at each of these signal levels and the error that will result in the conversion of the actual signal to sampled signal value. We say "possible outputs" because we are assuming that the ADC will output either the value immediately above or below the actual input signal level.

| Signal  | Closest 8-Bit  | Hexadecimal |              | Error as a Percent of |

|---------|----------------|-------------|--------------|-----------------------|

| Level   | Representation | Value       | Actual Error | Signal Level          |

| 0.50300 | 0.5000000      | 0x40        | 0.00300      | 0.596%                |

| 0.50300 | 0.5078125      | 0x41        | 0.0048128    | 0.957%                |

| 0.05030 | 0.0468750      | 0x06        | 0.003425     | 6.809%                |

| 0.05030 | 0.0546875      | 0x07        | 0.0043875    | 8.722%                |

| 0.00503 | 0.000000       | 0x00        | 0.00503      | 100%                  |

| 0.00503 | 0.0078125      | 0x01        | 0.0027825    | 55.32%                |

Table 3.1: Quantization effect with 8-bit signal

The actual error level remains more or less in the same range over the different signal ranges. This error level will fluctuate, depending on the exact signal value, but with our 8-bit signed example, the error level will always be less than 1/128, or 0.0087125. This fluctuating error

signal will be seen as a form of noise, or unwanted signal, by the DSP system. It is called quantization noise.

When the signal level is fairly large for the allowable range (0.503 is close to one half the maximum value), the percentage error is small = less than 1%. As the signal level gets smaller, the error percentage gets larger, as the table shows.

The quantization noise is always present and is, on average, the same level (any noise-like signal will rise and fall randomly, so we usually concern ourselves with the average level). But as the input signal decreases in level, the quantization noise becomes more significant in a relative sense. Eventually, for very small input signal levels, the quantization noise can become so significant that it degrades the quality of whatever signal processing is to be performed. Think of it as like static on a car radio. As you get farther from the radio station, the radio signal gets weaker, and eventually the static noise makes it difficult or unpleasant to listen to, even if you increase the volume.

So what can we do if our signal sometimes is strong (e.g., 0.503) and other times is weak (e.g., 0.00503)? Another way of saying this is that the signal has a large dynamic range. The dynamic range describes the ratio between the largest and smallest value of the signal—in this case, 100.

Suppose we exchange our 8-bit ADC for a 16-bit ADC? Then our maximum range is still from 1 to +1, but our step size is now 1/32,768, which works out to 0.000030518. Let's make a 16-bit table similar to the 8-bit example.

| Signal  | Closest 16-Bit | Hexadecimal | Error as a Percent |                 |

|---------|----------------|-------------|--------------------|-----------------|

| Level   | Representation | Value       | Actual Error       | of Signal Level |

| 0.50300 | 0.5029907      | 0x4062      | 0.000009277        | 0.00185%        |

| 0.50300 | 0.5030212      | 0x4063      | 0.00002124         | 0.00422%        |

| 0.05030 | 0.0502930      | 0x0670      | 0.00000703         | 0.0140%         |

| 0.05030 | 0.0503235      | 0x0671      | 0.0000235          | 0.0467%         |

| 0.00503 | 0.005005       | 0xA4        | 0.0000251          | 0.499%          |

| 0.00503 | 0.0050354      | 0xA5        | 0.0000054          | 0.107%          |

| Table 3.2: | Quantization | effects | with | 16-bit | signal |

|------------|--------------|---------|------|--------|--------|

|------------|--------------|---------|------|--------|--------|

What a difference! The actual error is always less than our step size, 1/32,768. But the error as a percent of signal level is dramatically improved. This is what we usually care about in signal processing. Because of the much smaller step size of the 16-bit ADC, the quantization noise is much less, allowing even small signals to be represented with very good precision (<1%). Notice that even for our small signal level, 0.00503, the error is about 0.1%.

Another way of describing this scenario is to introduce the concept of signal-to-noise power ratio, or SNR. This ratio describes the power of the largest signal compared to the background noise. This can be very easily seen on a frequency domain or spectral plot of a signal. There can be many sources of noise, but for now, we are considering only the quantization noise introduced by the ADC sampling.

SNR is usually expressed in decibels (denoted dB), using a logarithmic scale. The SNR of an ideal ADC can be determined by the following equation:

$SNR_{quantization}(dB) = 6.02^*(number of bits) + 1.76$

Basically, for each additional bit of the ADC, 6 dB of SNR is gained. An 8-bit ADC is capable of representing a signal with an SNR of about 48 dB, a 12-bit ADC can do better at 72 dB, and a 16-bit ADC will give up to 96 dB. This accounts only for the effect of quantization noise; in practice there are other effects that also will degrade SNR in a system.

There is one last important point regarding decibels. They are very commonly used in many areas of digital signal processing subsystems. A decibel is simply a signal power ratio, similar to a percentage. But because of the extremely high ratios commonly used (a billion is not uncommon), it is convenient to express this amount logarithmically. The logarithmic expression also allow chains of circuits or signal processing operations, each with its own ratio (e.g., of output power to input power), to simply be added up to find the final ratio.

Where people commonly get confused is in differentiating between signal levels or amplitude (voltage if an analog circuit) and signal power. Power measurements are virtual in the digital world but can be directly measured in analog circuits in which DSP systems interface with.

Two definitions of dB are commonly used:

$dB_{voltage} = dB_{digital \ value} = 20 \cdot \log(voltage \ signal \ 1/voltage \ signal \ 2)$  $dB_{power} = 10 \cdot \log(power \ signal \ 1/power \ signal \ 2)$

The designations "signal 1" and "signal 2" depend on the situation. For an RF power amplifier, the dB of gain will be 10 log (output power/input power). For an ADC, the dB of SNR will be 20 log (maximum input signal/quantization noise signal level). For a DAC, the dB of spurious free dynamic range will be 20 log (maximum output signal level/largest unwanted frequency component level generated by DAC circuits).

So dB can refer to many different ratios. But it is easy to get confused whether to use to the multiplicative factor of 10 or 20 without understanding the reasoning behind this.

Voltage squared is proportional to power. If a given voltage is doubled in a circuit, it requires four times as much power. This can be easily derived from the basic Ohm's law equation:

Power = Voltage<sup>2</sup>/Resistance

In many analog circuits, signal power is used because that is what the lab instruments work with, and while different systems may use different resistance levels (which affects voltage), power is universal (however, 50 ohm is the most common standard in most analog systems).

The important point is that since voltage is squared, this effect needs to be taken into account in the computation of logarithmic decibel relation. Remember,  $\log x^y = y \log x$ . Hence, the multiplication factor of 2 is required for voltage ratios, changing the 10 to a 20.

In the digital world, the concepts of resistance and power do not exist. A given signal has specific amplitude, expressed in a digital numerical system (such as signed fractional or integer, for example).

Understanding dB increases using the two measurement methods is important. Let's look at doubling of the amplitude ratio and doubling of the power ratio:

6.02 dB<sub>voltage</sub> = 6.02 dB<sub>digital value</sub> =  $20 \cdot \log(2/1)$ 3.01 dB<sub>power</sub> =  $10 \cdot \log(2/1)$

This is why shifting a digital signal left 1 bit (multiply by 2) causes a 6 dB signal power increase, and why so often the term 6 dB/bit is used in conjunction with ADCs, DACs, or digital systems in general.

By the same reasoning, doubling in power to a radio frequency (RF) engineer means a 3 dB increase. This will also impact the entire system. Coding gain, as used with error correcting code methods, is based on power. All signals at antenna interfaces are defined in terms of power, and the decibels used will be power ratios.

In both systems, ratios of equal power or voltage are 0 dB. For example, a unity gain amplifier has a gain of 0 dB:

$$0 \, \mathrm{dB}_{\mathrm{power}} = 10 \cdot \log(1/1)$$

A loss would be expressed as a negative dB—for example, a circuit whose output is equal to  $\frac{1}{2}$  the input power:

$$3.01 \text{ dB}_{power} = 10 \cdot \log(1/2)$$

# **Frequency Response**

When we have a sampled digital signal, we are ready to perform digital signal processing on this signal. In the preceding chapter, we briefly touched on representing the signal in the frequency domain. Usually, our goal is to modify the signal's frequency representation. This is normally performed using a filtering function. This is probably the most fundamental of DSP functions. In the previous example of the telephone system, we talked about sampling the voice signal at 8 kHz. Let's say we want to build an automated system to detect touch tones (on a touch-tone phone, whenever you press a number key, the phone creates two specific tones or frequencies in the audio signal band; i.e., what you hear when pressing the button). We could build a digital filter for each of the possible tones, feed the sampled audio signal into each filter, and monitor the outputs of the filters. In this way, we could detect when the telephone user presses the buttons, and which buttons are pressed, which is exactly what touch-tone phone systems do.

### 4.1 Frequency Response and the Complex Exponential

In this chapter, we discuss the concept of frequency response. Then in the next chapter, we will develop a way to relate a filter's frequency and time response. First, let's begin with an intuitive way to understand the frequency response of a filter. From the preceding chapter, we learned that we can create a complex exponential signal, which is just a positive or negative frequency rotation about the unit circle (radius = 1). Furthermore, when the frequency of the complex exponential reaches the Nyquist frequency, we have reached the maximum frequency that can be represented for a given sampling rate.

A complex exponential signal has the following form:

$$e^{j\omega t} = \cos(\omega t) + j\sin(\omega t)$$

or

$$e^{j2f\pi} = \cos(2\pi ft) + j\sin(2\pi ft)$$

This is very similar to what we saw before. The earlier angle  $\Omega$  has been replaced by  $\omega t$  or by  $2\pi ft$ . The significance of this is that we are no longer representing a point or vector on the unit circle of the complex number plane (as determined by angle  $\Omega$ ). Now we are

Digital Signal Processing 101. DOI: 10.1016/B978-1-85617-921-8.00008-0

representing a time-varying signal. This signal will move about the unit circle with a rotational speed of  $\omega$  radians per second. For a given  $\omega$  (rotational speed), we can determine the position of the signal at any given point in time (denoted by "t").

The second equation is equivalent to the first, except the rotational speed is expressed in cycles (revolutions) per second, denoted by "f." Make sure you understand this concept before moving on because both forms will appear interchangeably in the DSP world:

| t represents time, in seconds |  |

|-------------------------------|--|

|-------------------------------|--|

- $\omega$  represents rotational speed, in rad/s ( $2\pi$  radians = 1 revolution)

- f represents rotational speed, in cycles (or revolutions) per second

The variables  $\omega$  and f simply describe the same thing, using different units, like inches and centimeters. Recall that it takes exactly  $2\pi$  radians to complete a full circle. So 1 cycle/s equals  $2\pi$  rad/s, or  $\omega = 2\pi f$ .

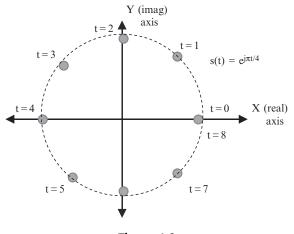

Both  $\omega$  and f denote the rotational speed in the counterclockwise direction. A negative value for  $\omega$  or f means we are rotating in the opposite direction (clockwise). Let's now consider an example. Let the rotational speed equal to 1/8 of a circle per second (it takes 8 s to complete 1 revolution). Therefore, f = 1/8. Also,  $\omega = 2\pi f$  or  $\omega = \pi/4$ . This signal (let's call it "s") can be described as follows:

$$\mathbf{s}(\mathbf{t}) = e^{j\pi t/4} = \cos(\pi t/4) + j\,\sin(\pi t/4)$$

We can evaluate s(t) at any given time t. For example, see Table 4.1.

| Time (s) | $s(t) = e^{j\pi t/4}$ | Angle of s(t) ( $^{\circ}$ ) | Angle of s(t) (rad) |

|----------|-----------------------|------------------------------|---------------------|

| 0        | 1                     | 0                            | 0                   |

| 1        | 0.707 +0.707j         | 45                           | $\pi/4$             |

| 2        | j                     | 90                           | π/2                 |

| 3        | 0.707 +0.707j         | 135                          | $3\pi/4$            |

| 4        | 1                     | 180                          | π                   |

| 5        | 0.707 0.707j          | 225                          | $5\pi/4 = 3\pi/4$   |

| 6        | j                     | 270                          | $3\pi/2 = \pi/2$    |

| 7        | 0.707 0.707j          | 315                          | $7\pi/8 = \pi/4$    |

| 8        | 1                     | 360 = 0                      | $2\pi = 0$          |

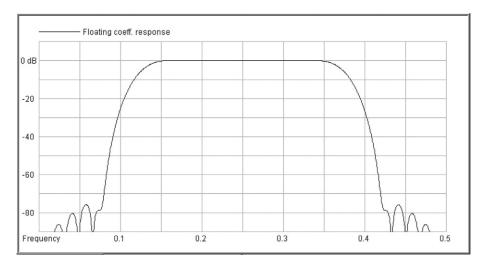

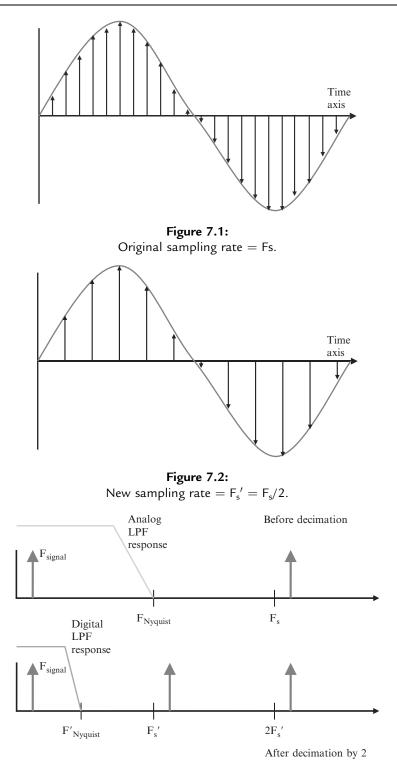

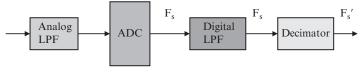

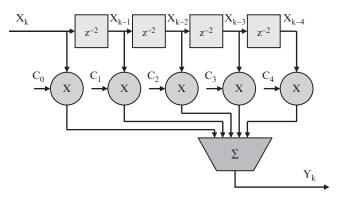

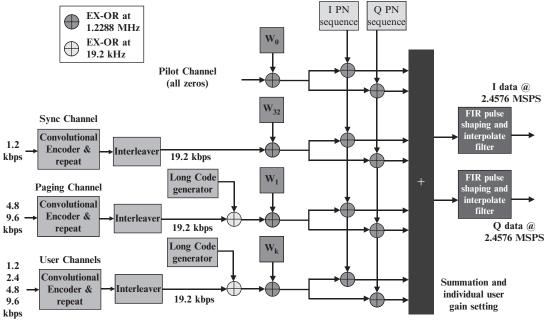

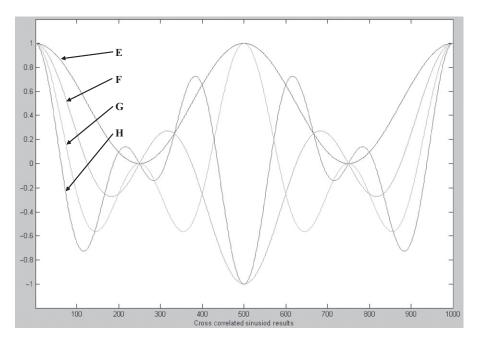

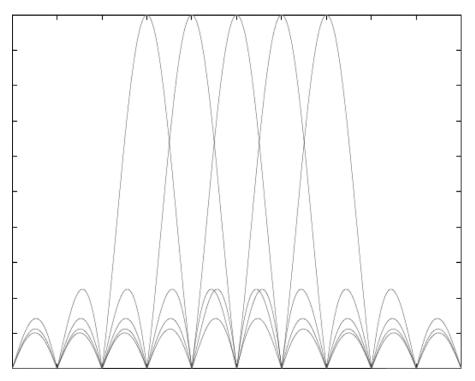

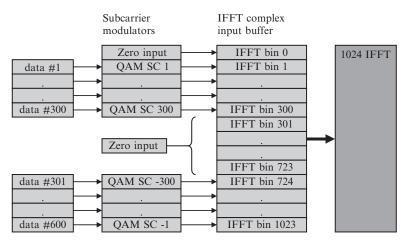

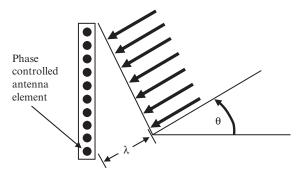

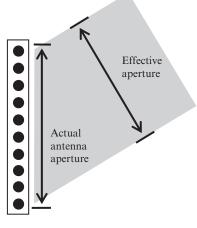

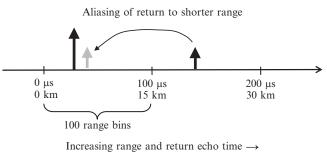

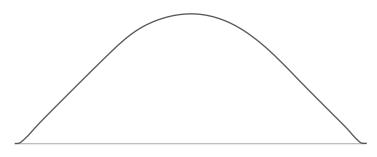

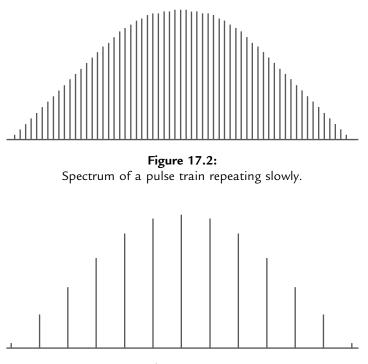

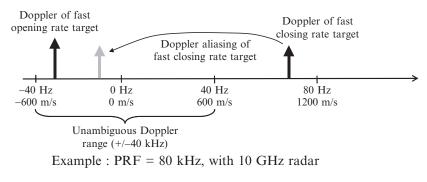

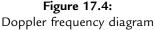

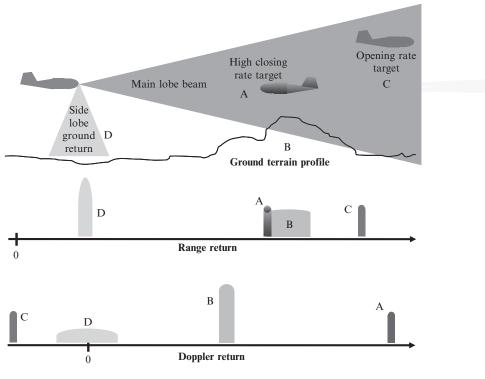

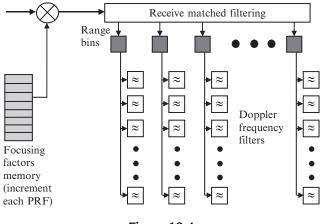

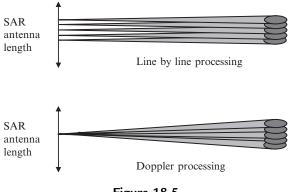

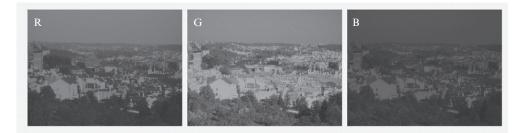

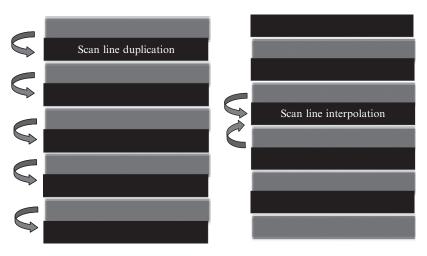

Table 4.1: Angular motion of complex exponential