# DIGITAL DESIGN AND COMPUTER ORGANIZATION

## Hassan A. Farha

CRC) CRC PRESS

Also available as a printed book see title verso for ISBN details

## DIGITAL DESIGN AND COMPUTER ORGANIZATION

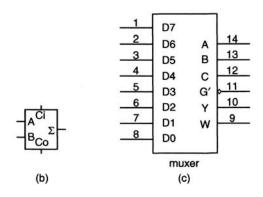

## DIGITAL DESIGN AND COMPUTER ORGANIZATION

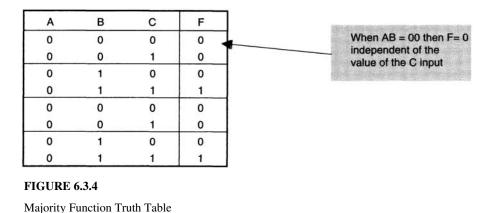

HASSAN A.FARHAT

Boca Raton London New York Washington, D.C.

This edition published in the Taylor & Francis e-Library, 2005.

"To purchase your own copy of this or any of Taylor & Francis or Routledge's collection of thousands of eBooks please go to www.eBookstore.tandf.co.uk."

#### Library of Congress Cataloging-in-Publication Data

Farhat, Hassan A. Digital design and computer organization/Hassan A.Farhat. p. cm. Includes index. ISBN 0-8493-1191-8 (alk. paper) 1. Digital electronics. 2. Logic circuits—Design and construction. 3. Computer organization. I. Title. TK7868.D5F37 2004 004.2 2–dc22 2003055805

This book contains information obtained from authentic and highly regarded sources. Reprinted material is quoted with permission, and sources are indicated. A wide variety of references are listed. Reasonable efforts have been made to publish reliable data and information, but the author and the publisher cannot assume responsibility for the validity of all materials or for the consequences of their use.

Neither this book nor any part may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, microfilming, and recording, or by any information storage or retrieval system, without prior permission in writing from the publisher.

The consent of CRC Press LLC does not extend to copying for general distribution, for promotion, for creating new works, or for resale. Specific permission must be obtained in writing from CRC Press LLC for such copying.

Direct all inquiries to CRC Press LLC, 2000 N.W. Corporate Blvd., Boca Raton, Florida 33431.

**Trademark Notice:** Product or corporate names may be trademarks or registered trademarks, and are used only for identification and explanation, without intent to infringe.

#### Visit the CRC Press Web site at www.crcpress.com

© 2004 by CRC Press LLC

No claim to original U.S. Government works

ISBN 0-203-48669-2 Master e-book ISBN

ISBN 0-203-58540-2 (Adobe eReader Format) International Standard Book Number 0-8493-1191-8 (Print Edition)

Library of Congress Card Number 2003055805

## **Dedication**

TO MY FATHER

## Acknowledgment

Sincere thanks go to the two acquiring editors from CRC Press: Nora Konopka as the main editor and Gerald Papke for his initial letter of encouragement and early correspondence. Nora's deadline extensions and kindness have made this task a reality. Many thanks for all their help go to the textbook's project editor, Gerry Jaffe, as well as to Jamie Sigal, Dawn Snider, and the other staff members who worked on the textbook.

Thanks to the staff of Electronics Workbench for supplying the software to be used with the text: in particular, Ian Suttie, vice president of sales, Joan Lewis-Milne, director of educational marketing, Scott Duncan, and the technical support staff that tested the circuits.

Thanks go to my students for their various inputs. Finally, sincere thanks and love go to my wife, son, and daughter for their encouragement, help, and understanding during the many hours it took to complete the textbook.

## Preface

*Digital Design and Computer Organization* is an introduction to digital design with application to computer organization. The tools studied in the text are used in the design of digital systems. Many systems today are digital in nature. This includes digital cameras and digital computers, for example. The book is suitable for students majoring in Computer Science, Electrical Engineering, and Computer Engineering. The contributions of the text are as follows:

- 1. The emphasis of the textbook is on logic design with minimal reference to electrical properties. This is an advantage to computer science students that have had no previous training in electrical engineering. The text assumes no previous knowledge of electrical components (elementary coverage is included and is optional). Electrical engineering students can also benefit from the textbook since, if needed, the topics can be complemented with lab supplements that consider electrical constraints.

- 2. Outside the use of a schematic capture tool used to simulate designs from primitive gates, the textbook is written to be vendor independent. Minimal coverage of actual chips and functionality is considered. As a result, the discussion is presented in general terms that emphasize the principles of digital design.

- 3. Topics are covered in the context of computer organization. The last two chapters of the text introduce instruction set architecture and present a complete design of a simple AC-based CPU. In this context students relate the principles of digital design studied to the topic of computer organization.

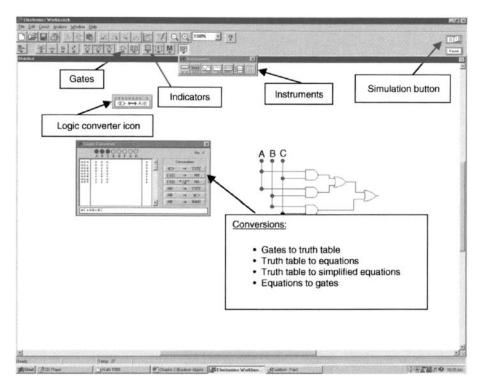

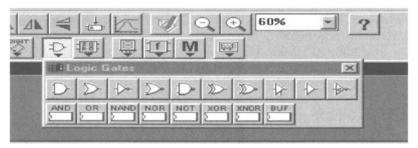

- 4. To enhance topics coverage, the majority of the circuits presented in the text are found in the accompanying CD. These circuits were designed and tested using the Electronics Workbench package. Many of the circuits found in the text are screen captures from the package. The Electronics Workbench package was chosen due to its friendly graphical-user interface. With minimal previous knowledge, the student can start the design process from truth tables, for example, and progress through the textbook to more complex design. The included circuits provide students the ability to simulate the functionality of the circuits in a hands-on fashion.

- 5. Topics are introduced in a gradual fashion. The coverage starts with simple cases and builds on these cases to introduce general cases.

Chapter 1 covers numbers representations and arithmetic in different bases. The topics covered include positional number systems, data types and ranges, conversion between the different bases, arithmetic in different bases, coding, and floating-point number representation. Radix complements and diminished radix complements are introduced. Arithmetic using this representation, however, is deferred until Chapter 5.

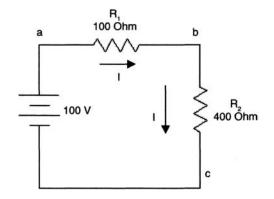

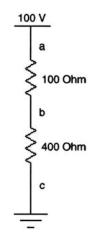

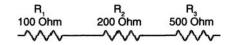

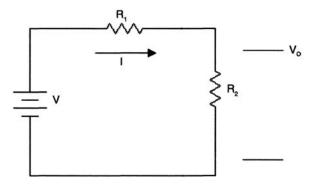

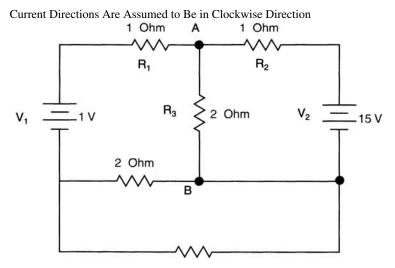

Chapter 2 includes introduction to Boolean algebra and its properties, algebraic simplification of Boolean expressions, gate representations in terms of design and analysis. In addition, the chapter includes elementary electrical topics. The concepts of voltage, current, and resistance are introduced. These are then followed with Kirchhoff's laws, voltage division, RC circuits, and applications in CMOS gate design.

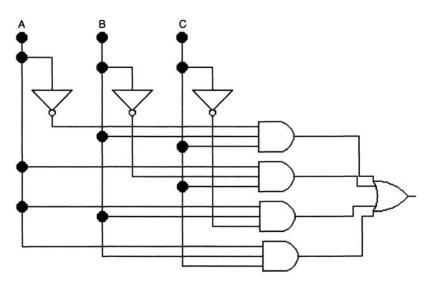

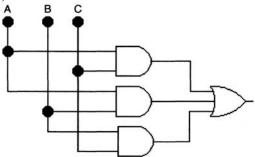

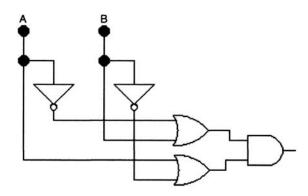

Chapter 3 begins with coverage of the canonical forms of Boolean functions and logical completeness. The design of circuits from canonical forms is considered; logical completeness is used to introduce additional gates and to introduce different two-level designs. Design automation tools and the Electronics Workbench are discussed.

Chapter 4 covers K-maps and the tabular method of minimizations for completely and incompletely specified functions. The chapter also includes multiple-output function minimization.

Chapter 5 deals with arithmetic and logic circuits. Topics covered include binary adders, look-ahead carry generators, magnitude comparators, binary subtractors, and multipliers. In addition, the chapter includes discussion of radix arithmetic, and allowable ranges are discussed in detail. The discussion includes the design of adders/subtractors based on the operands representation. The chapter concludes by designing an arithmetic logic unit in relation to computer organization. Bit-wise logic operations and multiplexers, as source selectors, are discussed in the context of the ALU (arithmetic logic unit) design.

Chapter 6 covers decoders, encoders, multiplexers, and demultiplexers. The design of Boolean functions, from decoder and multiplexers, and how to build larger units from smaller ones is covered. In addition, the chapter covers

programmable logic devices (Read Only Memory [ROM], Programmable Logic Array [PLA], and Programmable Array Logic<sup>®</sup> [PAL<sup>®</sup>]). The design using diodes as a conceptual realization at lower levels is given in the chapter as well. Here students can use the Electronics Workbench to experiment. Switches are included to simulate the process of programming the devices.

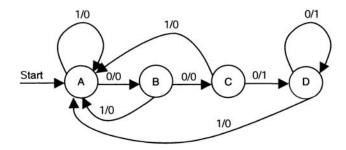

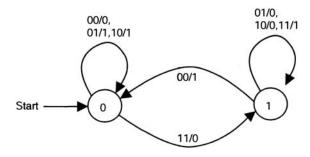

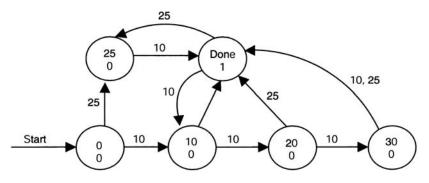

Chapter 7 starts the discussion of sequential circuits. It covers latches, latches behavioral description (characteristic tables, equations, state diagrams, and timing diagrams), gated latches, master-slave flip-flops, ones catching, edge-triggered flip-flops, and introduces sequential circuit analysis.

Chapter 8 covers the design of sequential circuits by relating it to analysis as covered in the previous chapter. Here, the constraints on the design are relaxed. Design based on excitation equations is given, followed by design from characteristic equations and design from word problems. The chapter includes discussions of the two machine representations, Mealy and Moore, and how one converts from one machine to the other. In addition, state minimization is covered in the chapter.

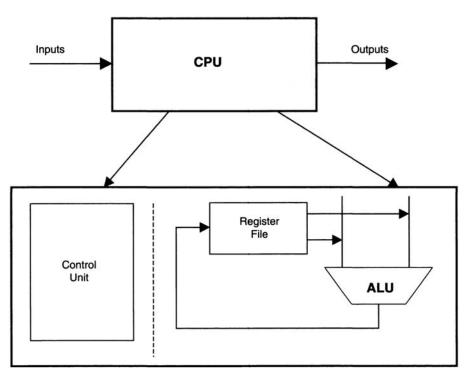

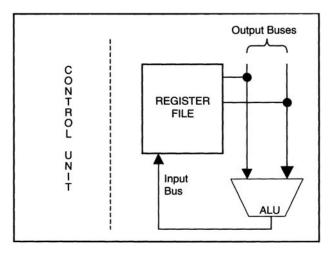

Chapter 9 includes the design of registers, counters, and general-purpose registers/counters. The chapter introduces memory design by designing larger memory from smaller memory first. This is then followed with design of memory cells and the internal design of a static RAM. The chapter concludes with a discussion of register files and relates the discussion to CPU organization and the ALU designed in Chapter 5.

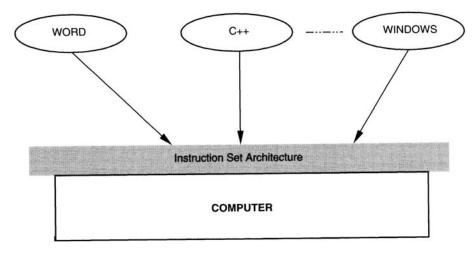

Chapter 10 is an introduction to instruction set architectures. Two different architectures (AC-based and general-purpose register-based) are discussed. Instructions formats in relation to both architectures are covered. Covered as well are translation of assembly instructions into machine instructions and the different addressing modes. Finally, the concept of macros as an alternative to hardware instructions is introduced. The homework section of this chapter includes discussion of stack-based instruction set architecture.

The book concludes with Chapter 11, where the design of a simple AC-based CPU is considered. To do this, we introduce the concept of a micro-operation and register-transfer languages. The design of register-transfer languages using direct connections and bus connections is then covered. This is followed with instruction set completeness, the instruction set of the AC-based CPU, the data-path and memory connections, and the control unit organization. The design of the CPU is then covered by considering the design of the combinational part of the control unit.

The instructor resources for the text include a solutions manual to the exercises given at the end of the chapters. This is in addition to a detailed set of lecture notes supplied in PowerPoint format.

The textbook is written to be suitable as 3-credit hour or 4-credit hour course. In a traditional 3-credit hour course, the minimal suggested topics coverage is Chapter 1 Chapter 2 (Sections 2.6 through 2.11 are optional) Chapter 3 Chapter 4 Chapter 5 Chapter 6 (Section 6.8 is optional) Chapter 7 Chapter 8 (optional) Chapter 9 (Sections 9.8 and 9.9 are optional)

The optional sections in Chapters 2 and 6 deal with the introductions to electrical circuits and designs of programmable logic devices using diodes. The intention is to give the reader with no electrical engineering background an elementary introduction to the topics. Chapter 8 deals with design of sequential circuits. Some instructors may cover the topic in a second digital course.

In a 4-credit hour course, the remaining chapters can be covered. This may be suitable in computer science curricula with two courses in the hardware area (digital design and computer architecture).

## Author

Hassan A.Farhat received his Ph.D. in Computer Science and Engineering in 1988 from the University of Nebraska at Lincoln. His research interests are in very-large-scale integration (VLSI) testing and computer graphics. Among the publications in VLSI testing, Dr. Farhat received best paper contributor award at the IEEE International Conference in Computer Design (ICCD) in 1988. His teaching interests are in the hardware track (digital design, computer organization, and computer architecture); VLSI testing; and computer graphics.

## Table of Contents

| 1      | Numbers in Different Bases                                             | 1  |

|--------|------------------------------------------------------------------------|----|

| 1.1    | Digital and Analog Data                                                | 2  |

| 1.2    | Coding                                                                 | 3  |

| 1.3    | Positional Number System                                               | 4  |

| 1.3.1  | Numbers without Radix Point                                            | 4  |

| 1.3.2  | Numbers with Radix Point                                               | 5  |

| 1.4    | Octal and Hexadecimal Bases                                            | 6  |

| 1.5    | Operands Types and Their Range                                         | 9  |

| 1.5.1  | Data Types                                                             | 10 |

| 1.5.2  | Finite Range                                                           | 10 |

| 1.6    | Conversion of Decimal Numbers to Equivalent Numbers in Arbitrary Bases | 12 |

| 1.6.1  | Conversion of Integer Part                                             | 13 |

| 1.6.2  | Converting the Fractional Part                                         | 14 |

| 1.7    | Binary Arithmetic                                                      | 16 |

| 1.7.1  | Addition                                                               | 16 |

| 1.7.2  | Subtraction                                                            | 19 |

| 1.7.3  | Multiplication                                                         | 20 |

| 1.8    | Radix and Diminished Radix Complements                                 | 22 |

| 1.9    | Representation of Negative Numbers                                     | 24 |

| 1.9.1  | The Three Representations                                              | 24 |

| 1.9.2  | Range of the Numbers                                                   | 26 |

| 1.10   | Coding and Binary Codes                                                | 27 |

| 1.10.1 | BCD Code                                                               | 28 |

| 1.10.2    | The Excess-m Code                                   | 28 |

|-----------|-----------------------------------------------------|----|

| 1.10.3    | Gray Code                                           | 30 |

| 1.10.4    | Character Codes                                     | 31 |

| 1.11      | Floating-Point Numbers                              | 32 |

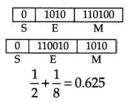

| 1.11.1    | Binary Representation of Floating-Point             | 32 |

| 1.11.2    | Normalized and Biased Floating-Point Representation | 34 |

| Chapter 1 | Exercises                                           | 35 |

| 2         | Boolean Algebra, and Gate and Transistor Design     | 37 |

| 2.1       | Boolean or Switching Algebra                        | 38 |

| 2.1.1     | Definitions                                         | 39 |

| 2.1.2     | Boolean Expressions                                 | 39 |

| 2.1.3     | Truth Tables                                        | 41 |

| 2.2       | Properties of Boolean Algebra                       | 43 |

| 2.2.1     | Axioms                                              | 43 |

| 2.2.2     | Principle of Duality                                | 44 |

| 2.3       | Simplification of Boolean Expressions               | 48 |

| 2.4       | Boolean Function                                    | 50 |

| 2.4.1     | Definitions                                         | 51 |

| 2.4.2     | Representations (Realization)                       | 52 |

| 2.4.3     | Complement of Boolean Functions                     | 54 |

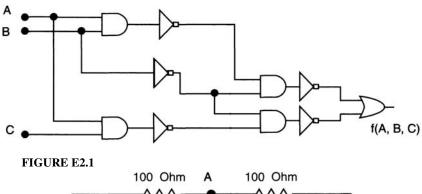

| 2.5       | Circuit Analysis and Gate Design                    | 55 |

| 2.5.1     | Circuit Analysis and Gate Representation            | 55 |

| 2.5.2     | Circuit Design                                      | 57 |

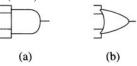

| 2.5.3     | Multiple Input Gates                                | 58 |

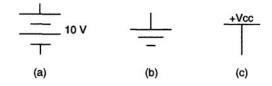

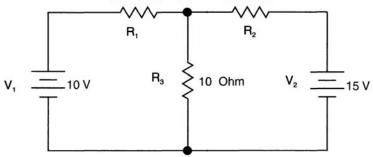

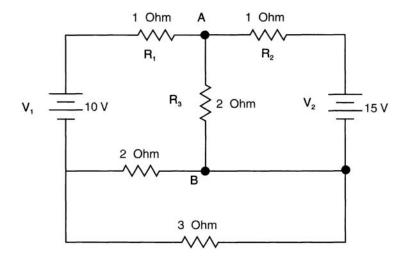

| 2.6       | Electrical Circuits                                 | 59 |

| 2.6.1     | Voltage, Current, and Resistance                    | 59 |

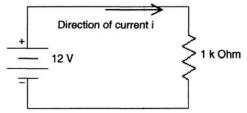

| 2.6.2     | Ohm's Law                                           | 60 |

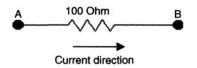

| 2.7       | Kirchhoff's Laws and Voltage Division               | 61 |

| 2.7.1     | Voltage Difference                                  | 61 |

| 2.7.2     | Kirchhoff's Voltage Law                                 | 62  |

|-----------|---------------------------------------------------------|-----|

| 2.7.3     | Voltage Division                                        | 63  |

| 2.8       | Kirchhoff's Current Law                                 | 66  |

| 2.9       | RC Circuits                                             | 70  |

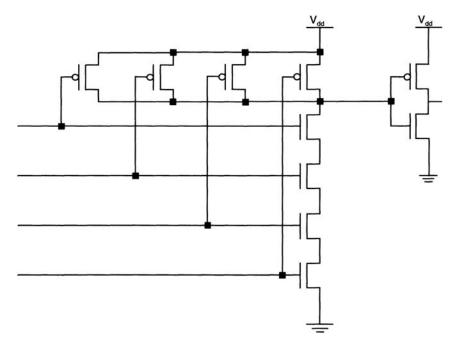

| 2.10      | Transistors and Logic Gates                             | 73  |

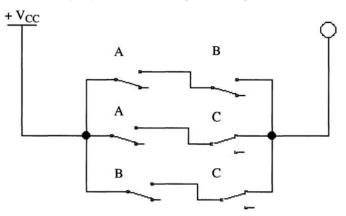

| 2.11      | CMOS Gate Design                                        | 76  |

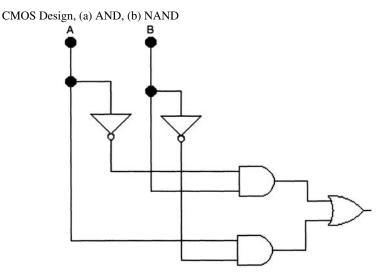

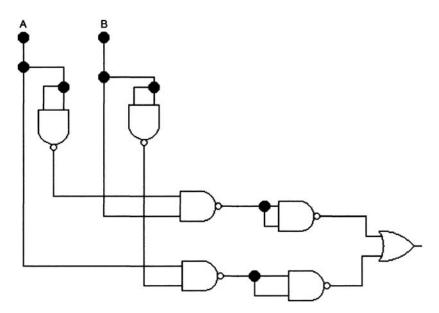

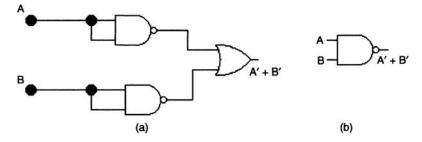

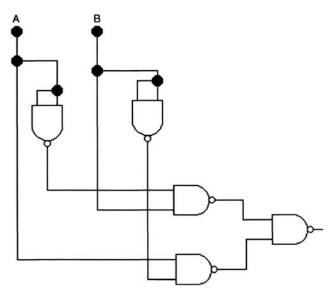

| 2.11.1    | The AND CMOS Design                                     | 78  |

| Chapter 2 | Exercises                                               | 78  |

| 3         | <b>Canonical Forms and Logical Completeness</b>         | 83  |

| 3.1       | Canonical Forms of Boolean Functions                    | 85  |

| 3.1.1     | Canonical Sum Form                                      | 85  |

| 3.1.2     | Canonical Product Form                                  | 90  |

| 3.2       | Sum of Product and Product of Sum Forms                 | 93  |

| 3.2.1     | Sum of Product Form                                     | 93  |

| 3.2.2     | Product of Sum Form                                     | 94  |

| 3.2.3     | Verification of Function Equality Using Canonical Forms | 95  |

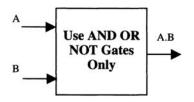

| 3.3       | Design of Functions in Standard Forms                   | 96  |

| 3.3.1     | Canonical Sum and Sum of Product Design                 | 96  |

| 3.3.2     | Canonical Product and Product of Sum Representation     | 97  |

| 3.4       | Other Two Variable Functions                            | 98  |

| 3.4.1     | Number of Boolean Functions over Two Variables          | 99  |

| 3.4.1.1   | The NAND Function                                       | 99  |

| 3.4.1.2   | The NOR Function                                        | 99  |

| 3.4.1.3   | The Exclusive OR Function                               | 100 |

| 3.4.1.4   | The Equivalence Function                                | 100 |

| 3.5       | Logical Completeness                                    | 101 |

| 3.5.1     | Definition and Examples                                 | 101 |

| 3.5.2     | The NAND and NOR Gates as Logically Complete Gates      | 102 |

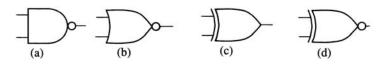

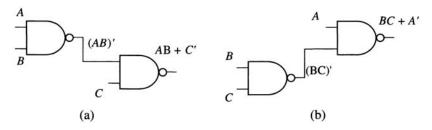

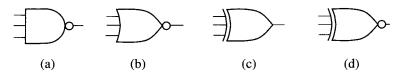

| 3.6       | HAND and NOR Design of Combinational Circuits           | 104 |

xiii

| 3.6.1     | NAND Gate Design                                  | 105 |

|-----------|---------------------------------------------------|-----|

| 3.6.2     | NOR Gate Design                                   | 105 |

| 3.6.3     | AND-OR-Invert and OR-AND-Invert Design            | 107 |

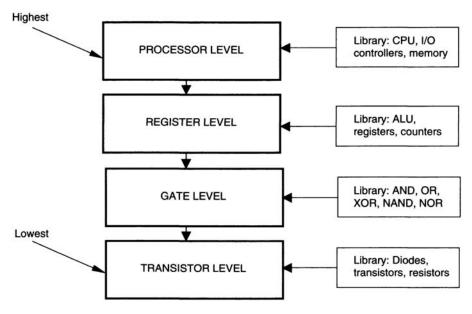

| 3.7       | Design Automation Tools and Levels of Abstraction | 108 |

| 3.7.1     | Levels of Abstraction                             | 109 |

| 3.7.2     | Computer-Aided Design (CAD) Tools                 | 110 |

| 3.7.2.1   | Design Entry                                      | 111 |

| 3.7.2.2   | Synthesis                                         | 112 |

| 3.7.2.3   | Simulation                                        | 113 |

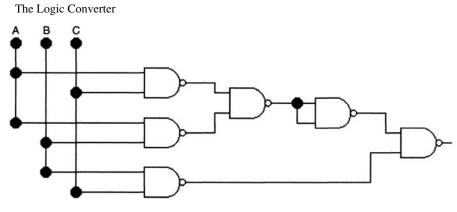

| 3.8       | Application to the Electronics Workbench (EW)     | 114 |

| 3.8.1     | The Electronics Workbench                         | 114 |

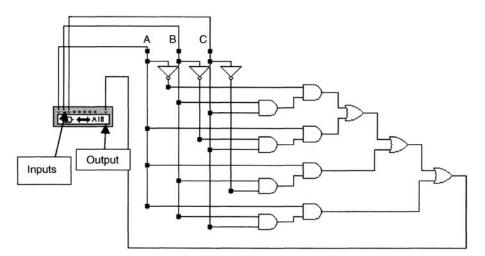

| 3.8.2     | Design Entry                                      | 115 |

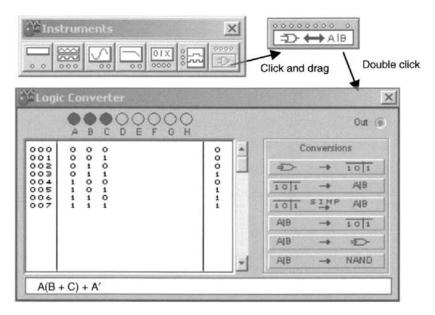

| 3.8.2.1   | Design Entry through Truth Tables                 | 116 |

| 3.8.2.2   | Design Entry through Equations                    | 117 |

| 3.8.2.3   | Design Entry Using Schematic Capture              | 117 |

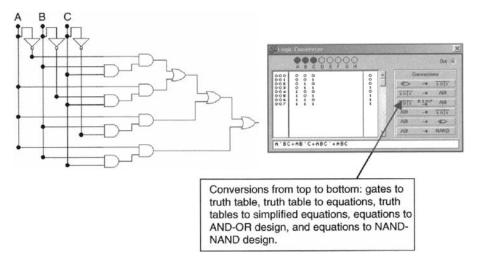

| 3.8.3     | Synthesis                                         | 120 |

| 3.8.3.1   | Synthesis from Truth Table                        | 121 |

| 3.8.3.2   | Synthesis from Equations                          | 122 |

| 3.8.3.3   | Synthesis from Schematic Capture                  | 122 |

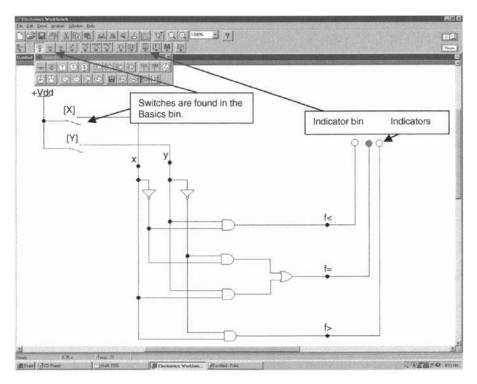

| 3.8.4     | Simulation                                        | 124 |

| 3.9       | Integrated Circuits                               | 126 |

| 3.9.1     | Small-Scale Integration                           | 127 |

| 3.9.2     | Medium-Scale Integration                          | 127 |

| 3.9.3     | Large-Scale Integration                           | 127 |

| 3.9.4     | Very-Large-Scale Integration                      | 128 |

| Chapter 3 | Exercises                                         | 129 |

| 4         | Minimization of Boolean Functions                 | 131 |

| 4.1       | Logical Adjacencies and K-Map Construction        | 132 |

| 4.1.1     | Logical Adjacency                                 | 132 |

| 4.1.2     | K-Map Construction                                       | 134 |

|-----------|----------------------------------------------------------|-----|

| 4.1.2.1   | The Inputs to the Table                                  | 135 |

| 4.1.2.2   | How Is the Table Read?                                   | 135 |

| 4.2       | Subcube Formations                                       | 136 |

| 4.2.1     | Filling the Table Entries                                | 136 |

| 4.2.2     | Subcubes and Minimization                                | 137 |

| 4.3       | K-Map Minimization                                       | 140 |

| 4.3.1     | Subcubes and Prime Implicants                            | 140 |

| 4.3.2     | K-Map Minimization                                       | 142 |

| 4.3.2.1   | Relationship to Subcubes on a K-Map                      | 143 |

| 4.3.2.2   | The Minimization Process                                 | 145 |

| 4.3.2.3   | Essential Prime Implicants and Examples                  | 146 |

| 4.4       | Incompletely Specified Functions                         | 149 |

| 4.5       | Product of Sum Minimization                              | 152 |

| 4.6       | The Quine-McCluskey or Tabular Method                    | 153 |

| 4.6.1     | Building Prime Implicants                                | 153 |

| 4.6.2     | Finding Minimal Cover                                    | 155 |

| 4.6.3     | Algorithmic Procedure of the Tabular Method              | 156 |

| 4.6.3.1   | Forming the Prime Implicants                             | 156 |

| 4.6.3.2   | Minimal Cover Procedure                                  | 159 |

| 4.6.4     | Decimal Method of Building Prime Implicants              | 161 |

| 4.7       | Multiple-Output Function Minimization                    | 162 |

| Chapter 4 | Exercises                                                | 167 |

| 5         | Arithmetic Logic Circuits and Programmable Logic Devices | 170 |

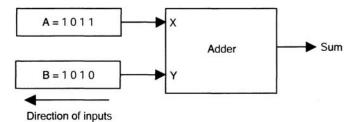

| 5.1       | Binary Adders                                            | 171 |

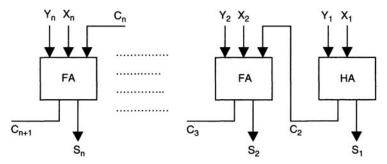

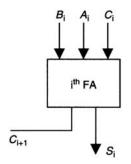

| 5.1.1     | Iterative Circuits                                       | 171 |

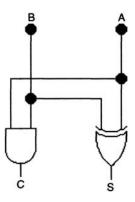

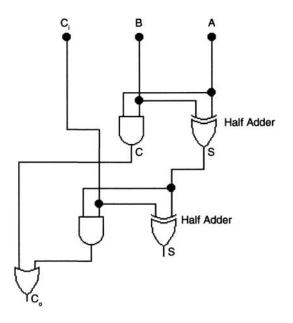

| 5.1.2     | Half and Full Adders                                     | 173 |

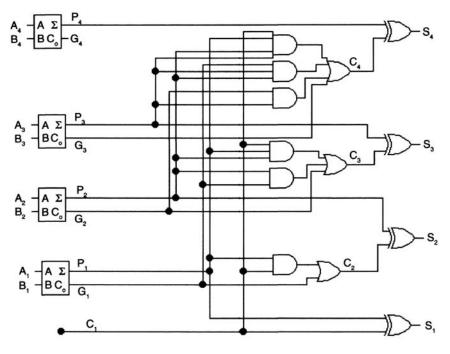

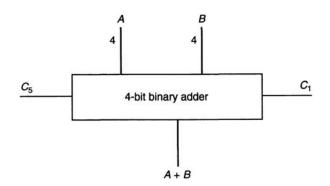

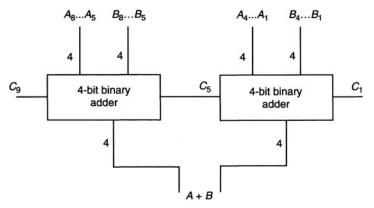

| 5.2       | Look-Ahead Carry Generators                              | 176 |

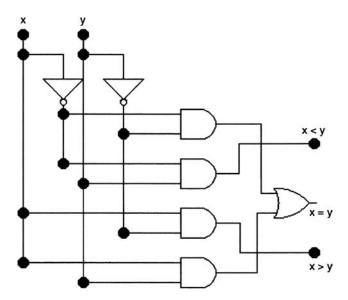

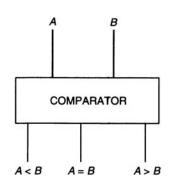

| 5.3       | Magnitude Comparators                                    | 178 |

xv

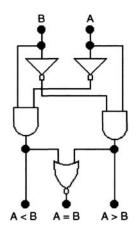

| 5.3.1       | 1-Bit Magnitude Comparator                      | 180 |

|-------------|-------------------------------------------------|-----|

| 5.3.2       | Boolean Equations for the Equal Output          | 180 |

| 5.3.3       | Design of the <i>A</i> > <i>B</i> Output        | 181 |

| 5.3.4       | Boolean Equations for <i>A</i> < <i>B</i>       | 181 |

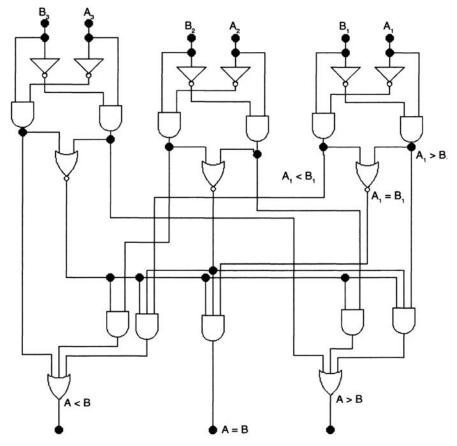

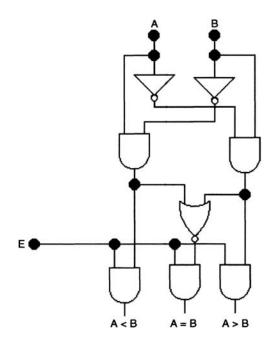

| 5.3.5       | Magnitude Comparators with Enable Lines         | 182 |

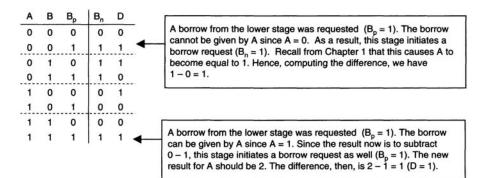

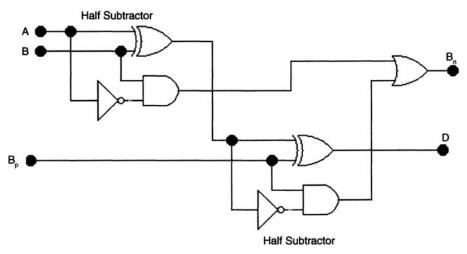

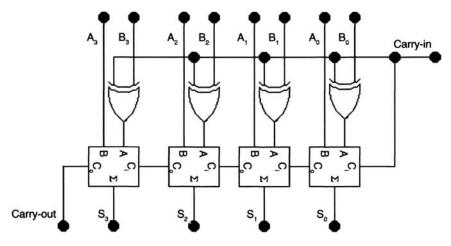

| 5.4         | Binary Subtracters                              | 182 |

| 5.4.1       | Half Subtracters                                | 182 |

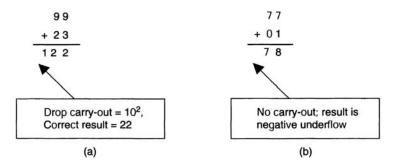

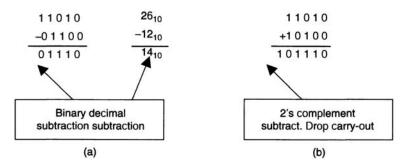

| 5.5         | Arithmetic Circuits Using Radix Complement      | 185 |

| 5.5.1       | Unsigned Addition and Subtraction               | 186 |

| 5.5.2       | Hardware Implementation of Unsigned Arithmetic  | 188 |

| 5.5.3       | Signed Number Arithmetic in Radix Complement    | 189 |

| 5.5.3.1     | An Alternative Method to Compute 2's Complement | 189 |

| 5.5.3.2     | Signed Arithmetic                               | 191 |

| 5.5.3.2.1 0 | Case One (No Overflow or Underflow Is Possible) | 191 |

| 5.5.3.2.2 0 | Case Two (Overflow Is Possible to Occur)        | 191 |

| 5.5.3.2.3 0 | Case Three (Underflow Is Possible to Occur)     | 192 |

| 5.5.4       | Hardware Implementation of Signed Arithmetic    | 192 |

| 5.6         | Multiplier Circuits                             | 194 |

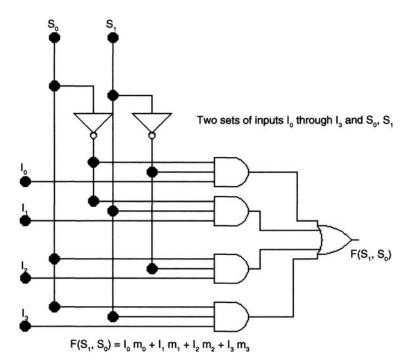

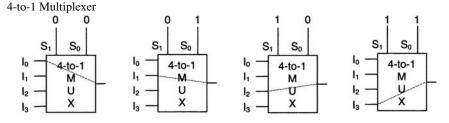

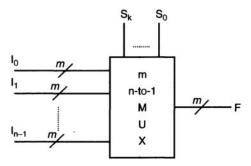

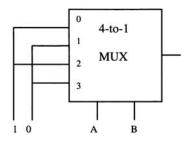

| 5.7         | Multiplexers                                    | 196 |

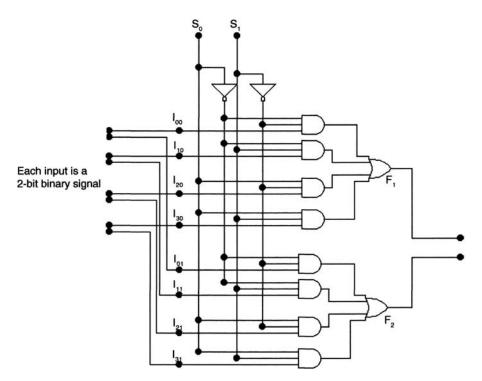

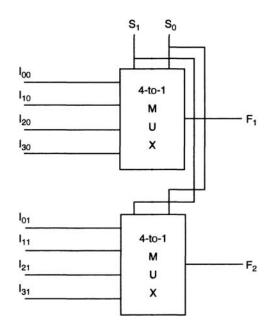

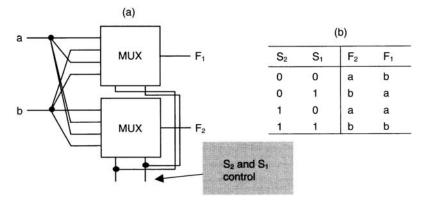

| 5.7.1       | Design of Multiple Output Multiplexers          | 198 |

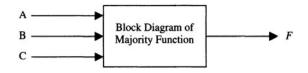

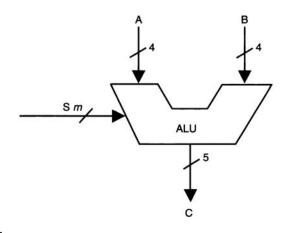

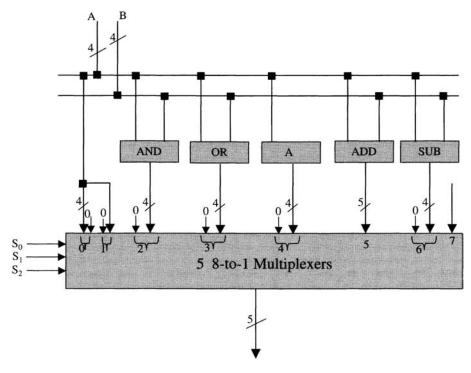

| 5.8         | Design of a Simple Arithmetic Logic Unit        | 198 |

| 5.8.1       | Subtraction and the Arithmetic Unit             | 199 |

| 5.8.2       | Bit-Wise Logic Operations                       | 201 |

| 5.8.3       | Combinational Shift Left                        | 201 |

| 5.8.4       | The Design of the ALU                           | 202 |

| Chapter 5   | Exercises                                       | 203 |

| 6           | Programmable Logic Devices                      | 207 |

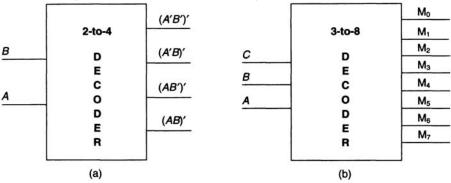

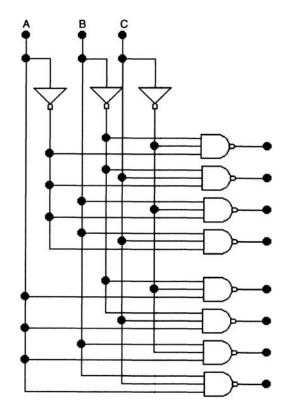

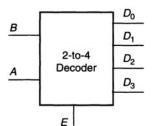

| 6.1         | Decoders                                        | 208 |

| 6.1.1       | Binary Decoders                                 | 208 |

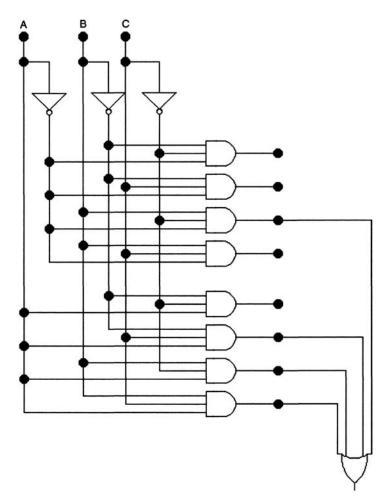

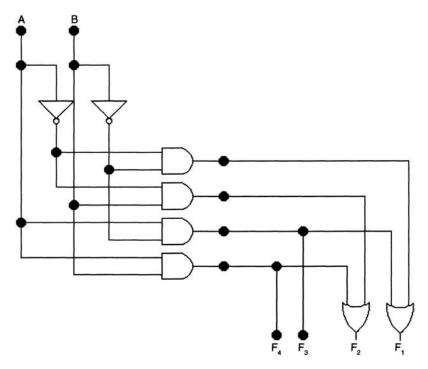

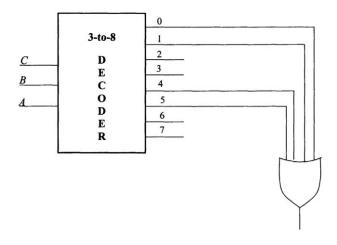

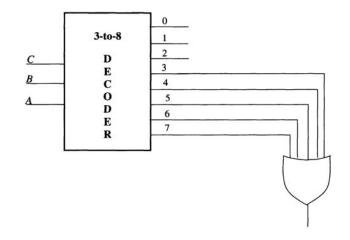

| 6.1.2     | Function Design Using Decoders                  | 212 |

|-----------|-------------------------------------------------|-----|

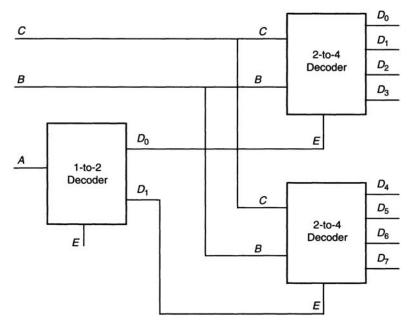

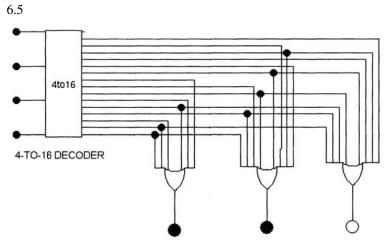

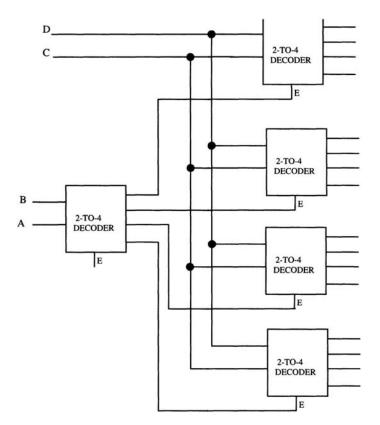

| 6.1.3     | Building Larger Decoders from Smaller Ones      | 215 |

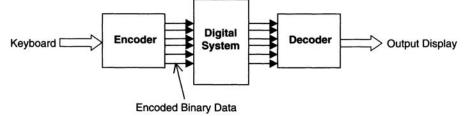

| 6.2       | Encoders                                        | 216 |

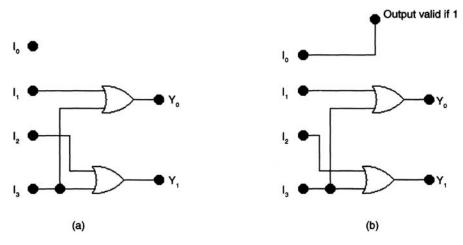

| 6.2.1     | Binary Encoders                                 | 217 |

| 6.2.2     | Priority Encoders                               | 219 |

| 6.3       | Multiplexers                                    | 220 |

| 6.3.1     | Design and Equations                            | 221 |

| 6.3.2     | Design of Larger Multiplexers from Smaller Ones | 221 |

| 6.3.3     | Design of Boolean Functions Using Multiplexers  | 222 |

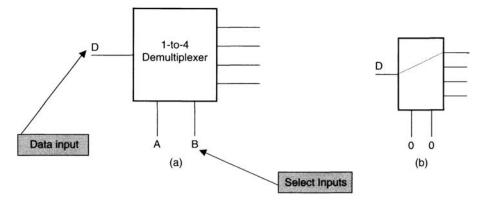

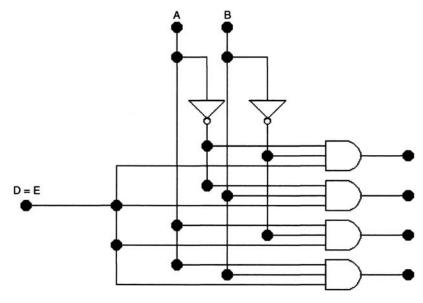

| 6.4       | Demultiplexers                                  | 226 |

| 6.5       | Programmable Logic Arrays                       | 227 |

| 6.5.1     | Programmable Logic Devices (PLDs)               | 227 |

| 6.5.2     | Programmable Logic Arrays                       | 229 |

| 6.5.3     | Tabular Description                             | 234 |

| 6.5.4     | AND-OR-NOT Design                               | 236 |

| 6.6       | Programmable Array Logic Devices                | 237 |

| 6.7       | Read-Only Memory                                | 240 |

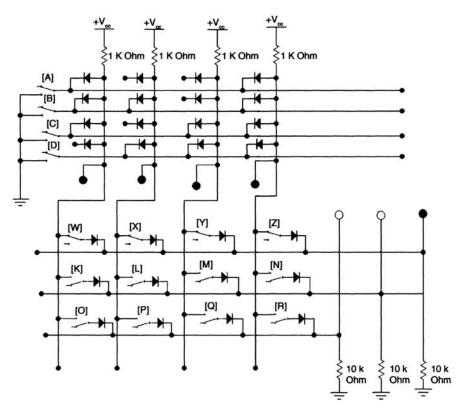

| 6.8       | Diodes and Programmable Logic Devices           | 242 |

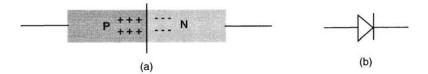

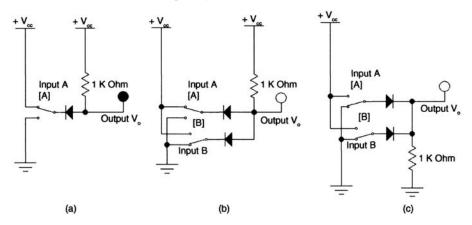

| 6.8.1     | Diodes                                          | 243 |

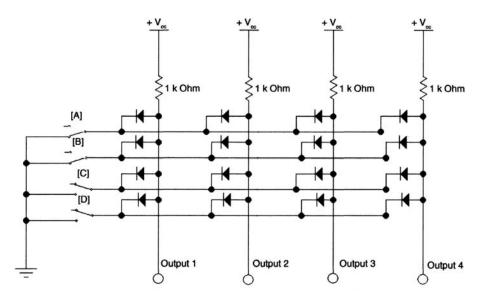

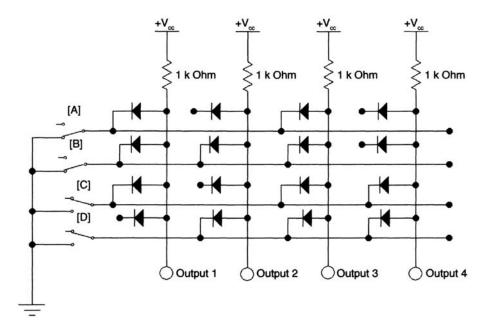

| 6.8.2     | Programmable Logic Devices                      | 245 |

| 6.8.3     | Diode Design of Programmable Logic Arrays       | 246 |

| Chapter 6 | Exercises                                       | 247 |

| 7         | Flip-Flops and Analysis of Sequential Circuits  | 250 |

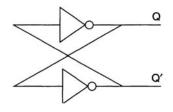

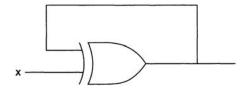

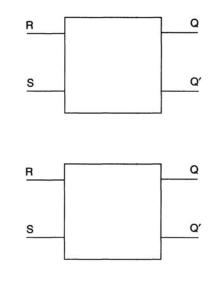

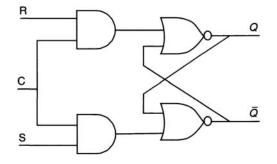

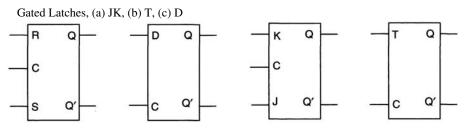

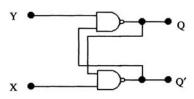

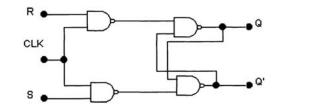

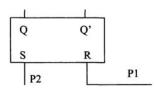

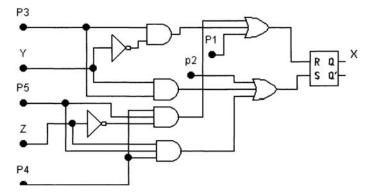

| 7.1       | Latches                                         | 252 |

| 7.1.1     | Feedback Loops                                  | 252 |

| 7.1.2     | SR Latches                                      | 253 |

| 7.2       | Behavioral Description                          | 256 |

| 7.2.1     | Characteristic Table                            | 256 |

| 7.2.2     | Characteristic Equations                        | 257 |

xvii

| 7.2.3  | State Diagrams                             | 257 |

|--------|--------------------------------------------|-----|

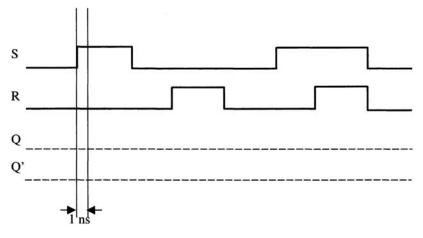

| 7.2.4  | Timing Diagrams                            | 258 |

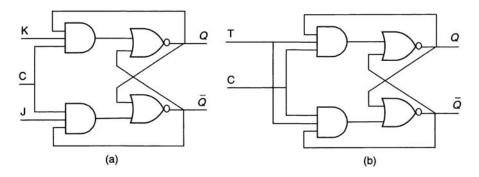

| 7.3    | Other Primitive Latches                    | 259 |

| 7.3.1  | Characteristic Tables of the Three Latches | 261 |

| 7.3.2  | The Characteristic Equations               | 261 |

| 7.3.3  | The State Diagrams                         | 262 |

| 7.4    | The Latches Gate Design                    | 262 |

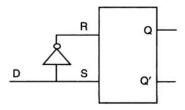

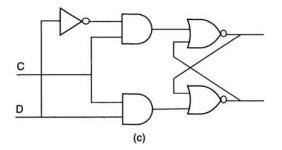

| 7.4.1  | D Latch Design                             | 262 |

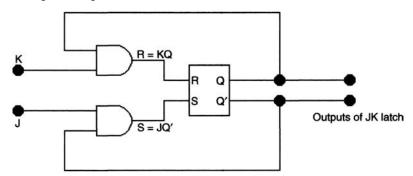

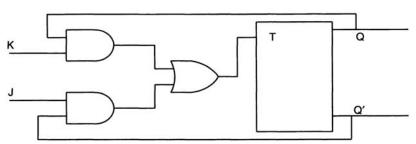

| 7.4.2  | The JK Latch                               | 262 |

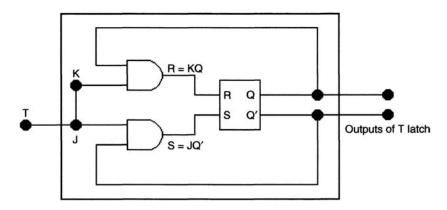

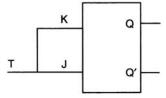

| 7.4.3  | The T Latch                                | 265 |

| 7.5    | Gated Latches                              | 265 |

| 7.6    | Flip-Flops                                 | 268 |

| 7.6.1  | Asynchronous and Synchronous Circuits      | 268 |

| 7.6.2  | Master-Slave Flip-Flops                    | 271 |

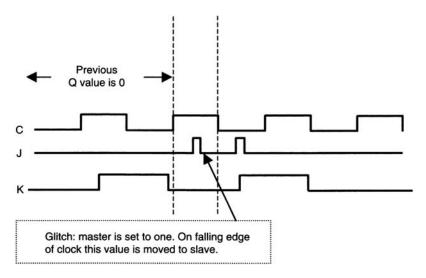

| 7.7    | Glitches and Ones-Catching                 | 271 |

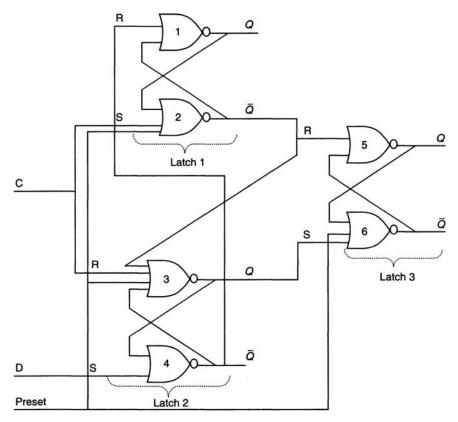

| 7.8    | Edge-Triggered Flip-Flops                  | 274 |

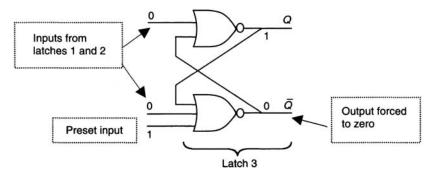

| 7.8.1  | Asynchronous Preset                        | 274 |

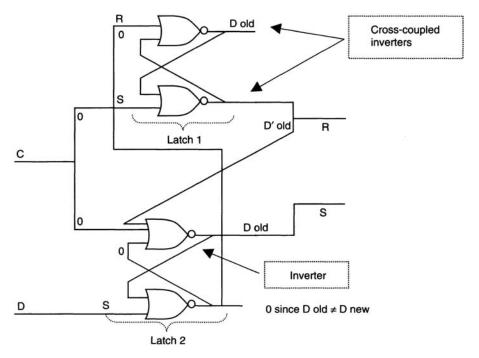

| 7.8.2  | Clock Value Equal to 1                     | 276 |

| 7.8.3  | Clock Makes a Transition from 1 to 0       | 277 |

| 7.8.4  | Clock Value Is 0                           | 277 |

| 7.8.5  | Clock Makes Transition from 0 to 1         | 278 |

| 7.9    | Block Diagrams and Timing Constraints      | 279 |

| 7.9.1  | Timing Constraints                         | 280 |

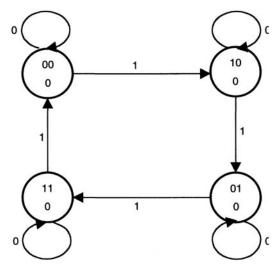

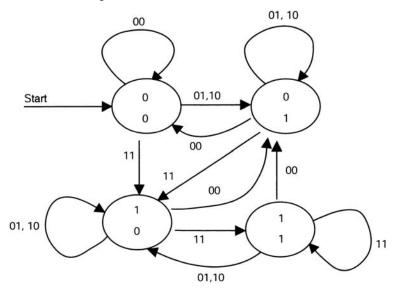

| 7.10   | Analysis of Sequential Circuits            | 281 |

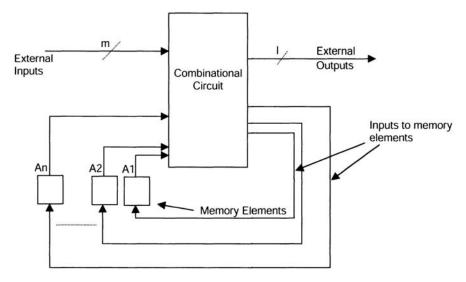

| 7.10.1 | Sequential Circuits Block Diagram Model    | 283 |

| 7.10.2 | Characteristic Equations                   | 284 |

| 7.10.3 | Characteristic or State Table Construction | 286 |

| 7.10.4 | State Diagrams                             | 287 |

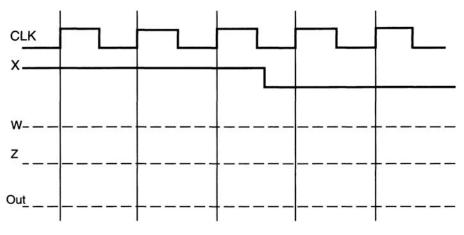

| 7.10.5 | Timing Diagrams                            | 289 |

| 7.10.6    | Alternative Representations of State Tables                                       | 293 |

|-----------|-----------------------------------------------------------------------------------|-----|

|           | 1                                                                                 |     |

| Chapter 7 | Exercises                                                                         | 294 |

| 8         | Design of Sequential Circuits and State Minimization                              | 298 |

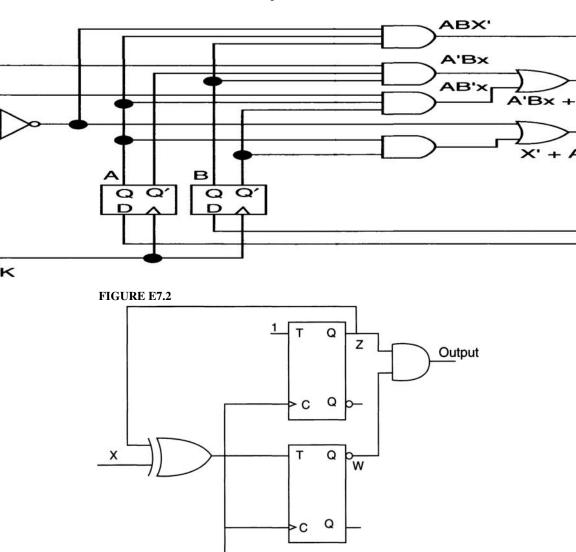

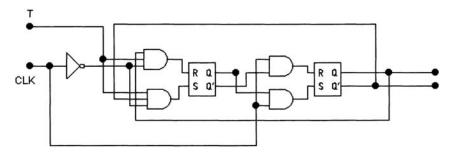

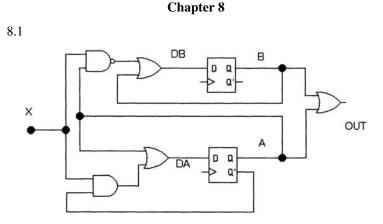

| 8.1       | Block Diagrams and Design from Excitation Equations                               | 300 |

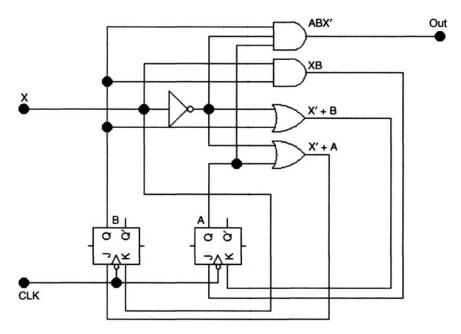

| 8.1.1     | Design of Sequential Circuits Given the External Outputs and Excitation Equations | 300 |

| 8.2       | Design Given the Characteristic Equations                                         | 302 |

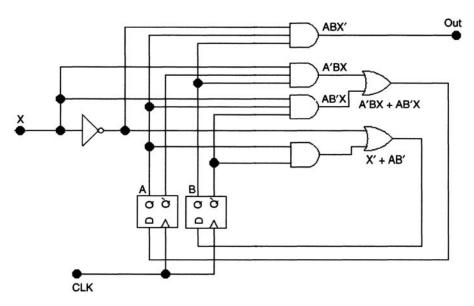

| 8.2.1     | Design Using D Flip-Flops                                                         | 302 |

| 8.2.2     | Design Using JK Flip-Flops                                                        | 304 |

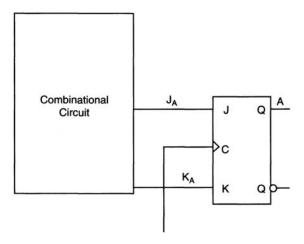

| 8.3       | General Design Procedure of Sequential Circuits                                   | 306 |

| 8.3.1     | Step 1                                                                            | 306 |

| 8.3.2     | Step 2                                                                            | 307 |

| 8.3.3     | Step 3                                                                            | 307 |

| 8.3.3.1   | Flip-Flop Excitation Tables                                                       | 309 |

| 8.3.4     | Step 4                                                                            | 310 |

| 8.3.5     | Step 5                                                                            | 311 |

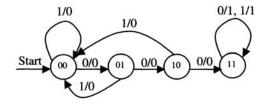

| 8.4       | Machine Equivalence and State Assignments                                         | 311 |

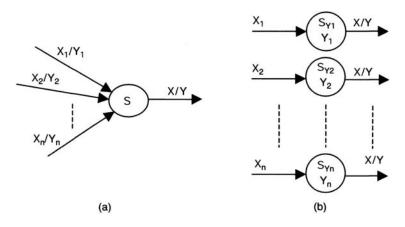

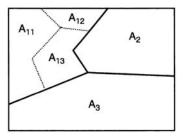

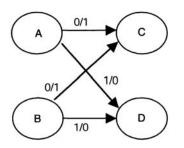

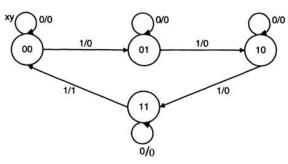

| 8.5       | Mealy State Diagrams                                                              | 316 |

| 8.6       | Moore Machines                                                                    | 321 |

| 8.6.1     | Conversion from Mealy to Moore Machines                                           | 323 |

| 8.7       | Machine and State Equivalence                                                     | 325 |

| 8.8       | State Reduction and Minimal State Diagrams                                        | 329 |

| 8.8.1     | The Reduced State Table                                                           | 333 |

| Chapter 8 | Exercises                                                                         | 333 |

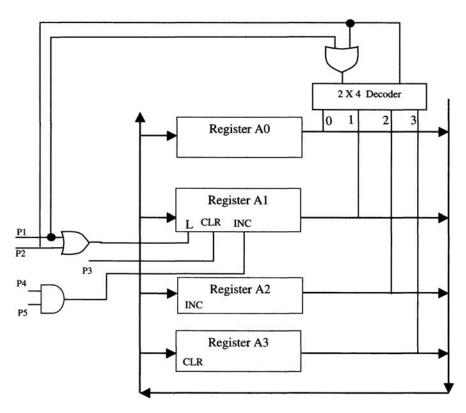

| 9         | Registers, Counters, and Memory Elements                                          | 337 |

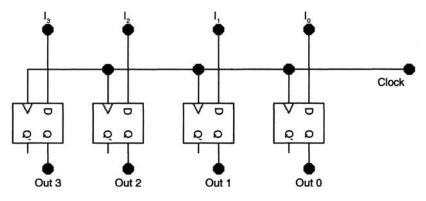

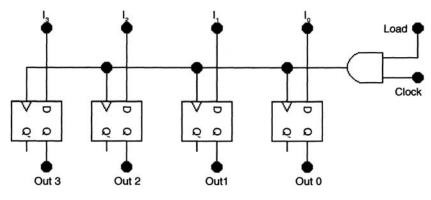

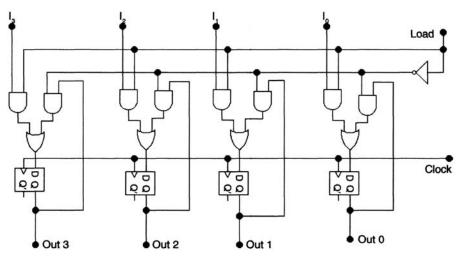

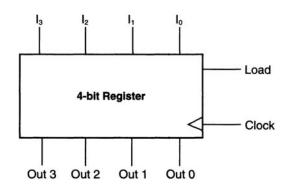

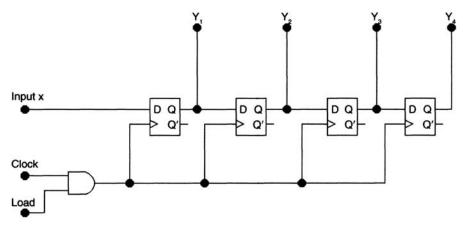

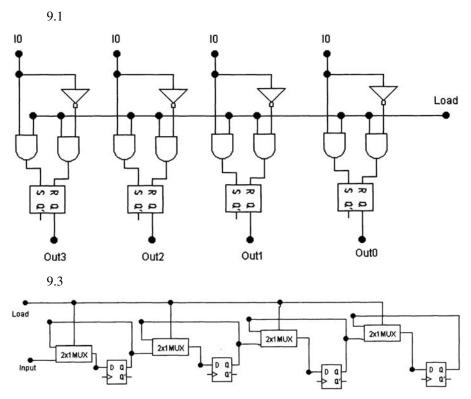

| 9.1       | Registers                                                                         | 338 |

| 9.1.1     | Parallel Registers                                                                | 338 |

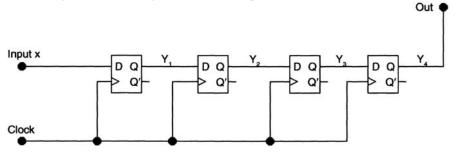

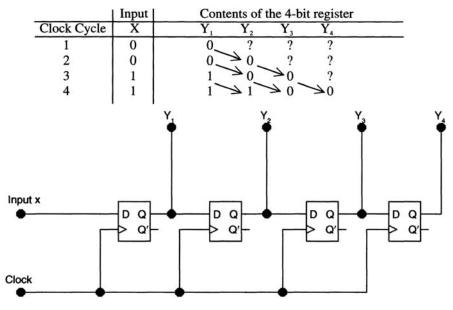

| 9.1.2     | Shift Registers                                                                   | 341 |

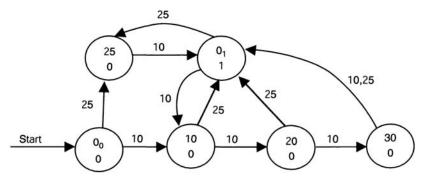

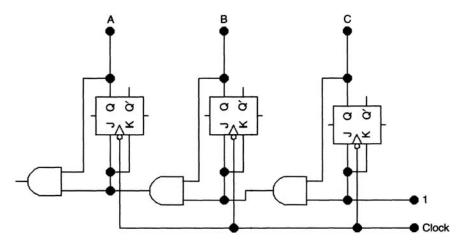

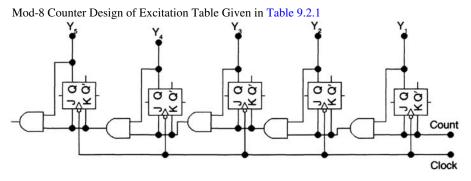

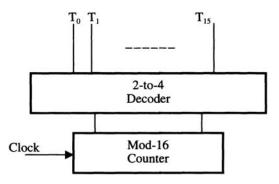

| 9.2       | Counters                                                                          | 343 |

| 9.2.1     | Mod-2 <sup>n</sup> Synchronous Counters                                           | 343 |

|           |                                                                                   |     |

xix

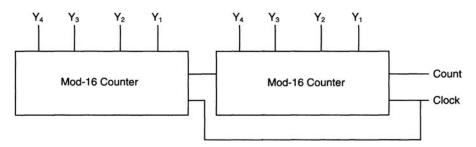

| 9.2.2     | Mod-M Counters for General M                   | 346 |

|-----------|------------------------------------------------|-----|

| 9.2.3     | Binary Counters with Decreasing Counts         | 348 |

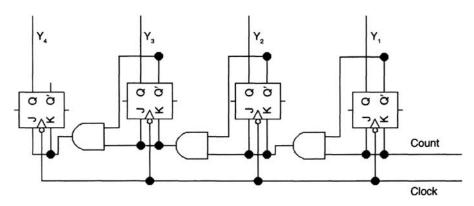

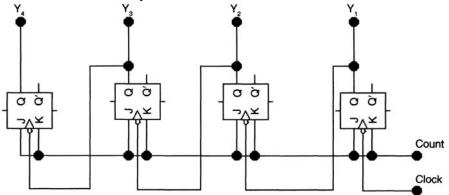

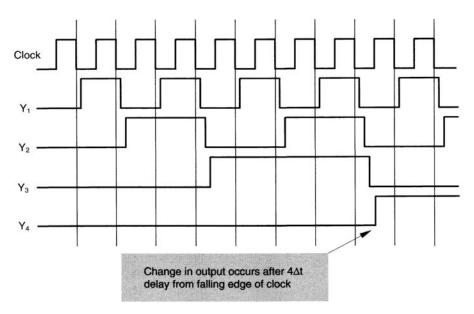

| 9.3       | Asynchronous, Ring, and Johnson Counters       | 350 |

| 9.3.1     | Asynchronous Counters                          | 350 |

| 9.3.2     | Ring Counters                                  | 351 |

| 9.3.3     | Johnson Counters                               | 352 |

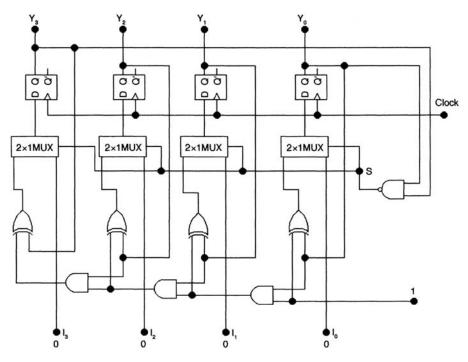

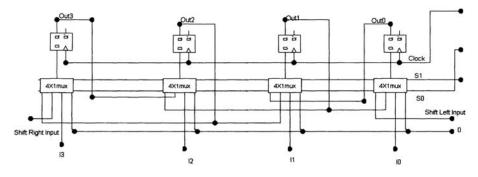

| 9.4       | General-Purpose Register-Counter Circuits      | 354 |

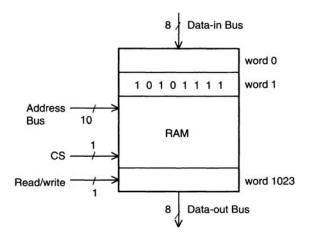

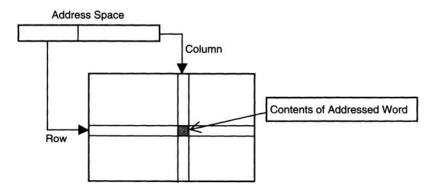

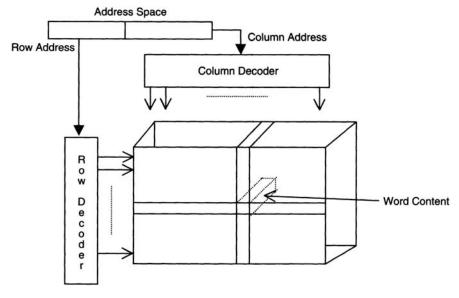

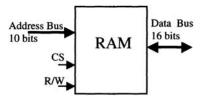

| 9.5       | Memory Block Diagram                           | 359 |

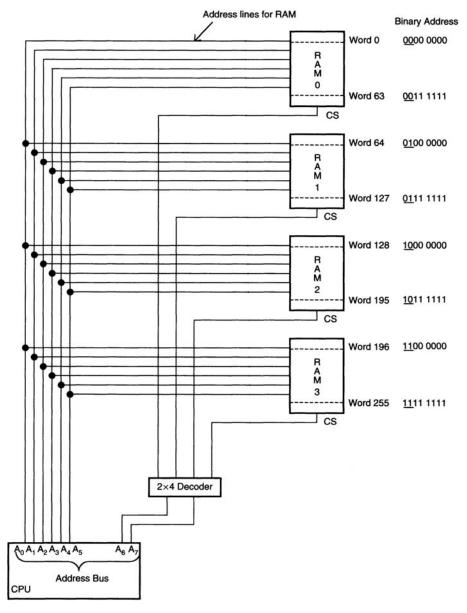

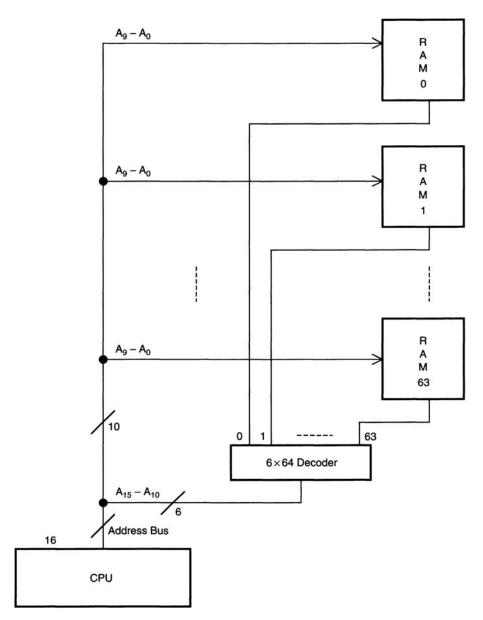

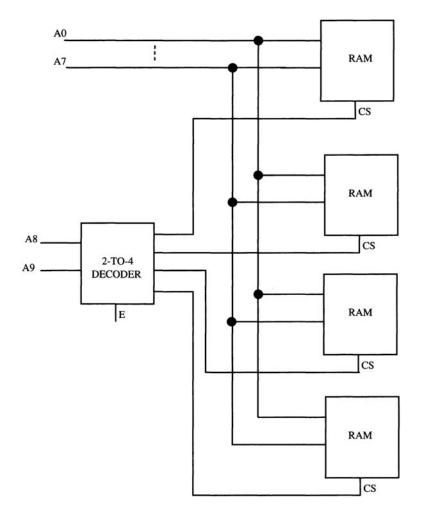

| 9.6       | Building Larger RAM from Smaller RAM           | 361 |

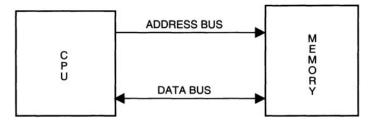

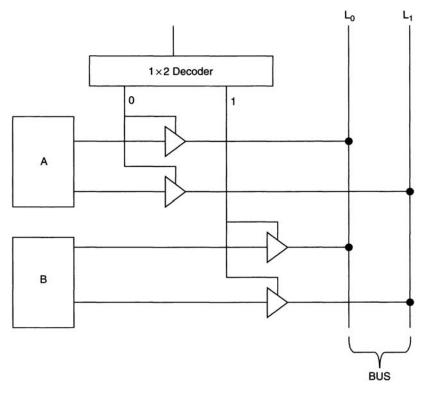

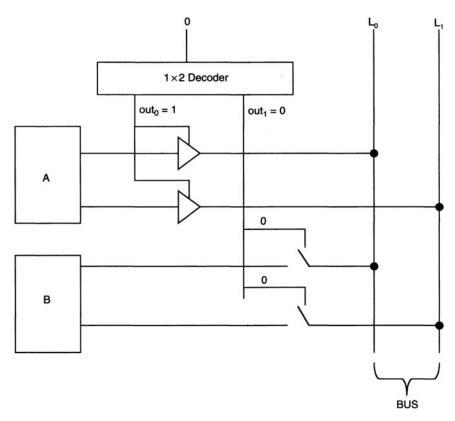

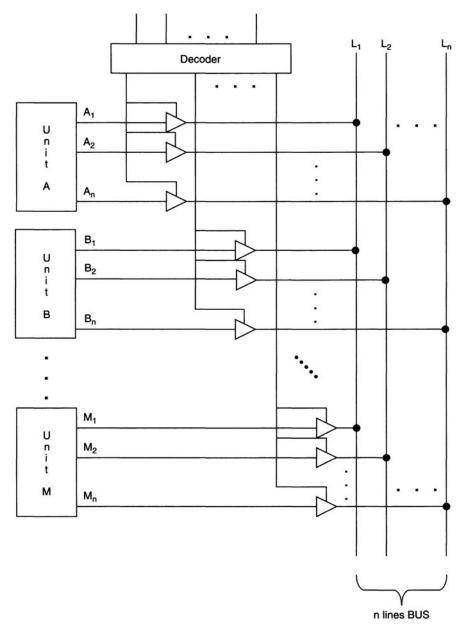

| 9.7       | The Data Bus Connections                       | 363 |

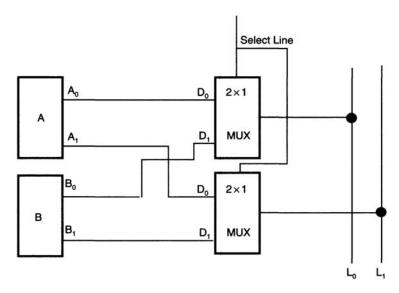

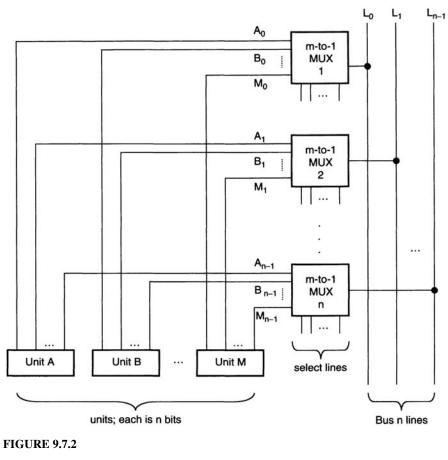

| 9.7.1     | Connections Using Multiplexers                 | 365 |

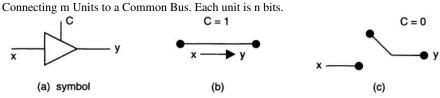

| 9.7.2     | Connections Using Tristate Gates               | 367 |

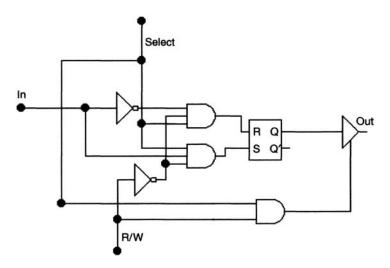

| 9.8       | Internal Design of Memory                      | 367 |

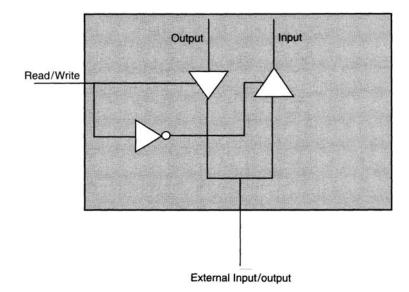

| 9.8.1     | Gate Design of a Single Memory Cell            | 367 |

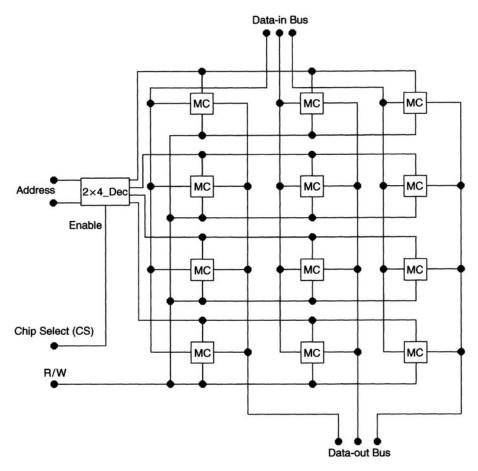

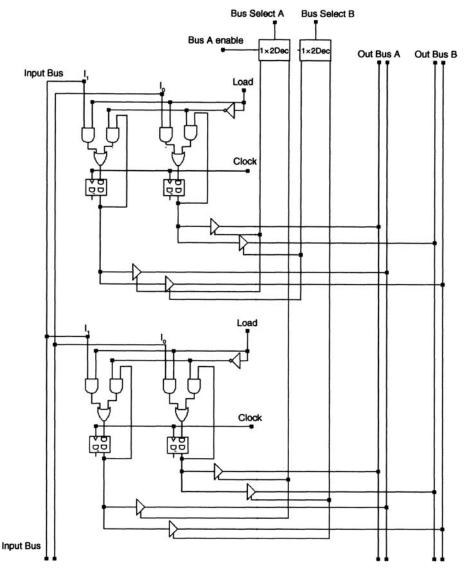

| 9.8.2     | RAM Design with Two Data Buses                 | 368 |

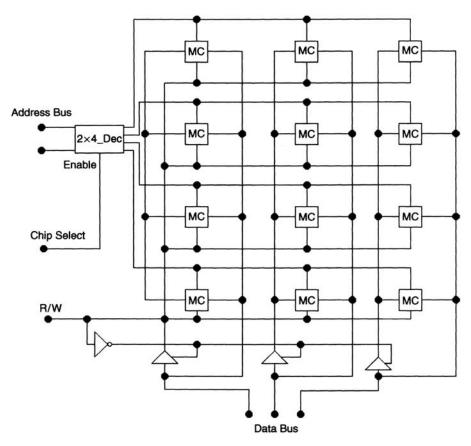

| 9.8.3     | RAM Design with a Single Data Bus              | 370 |

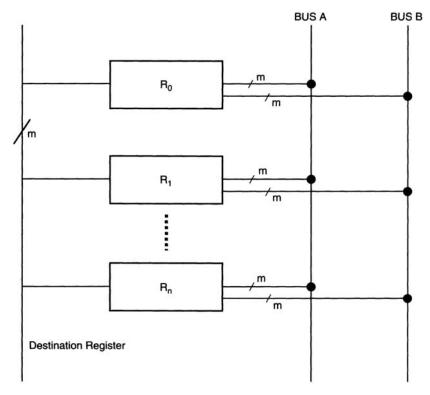

| 9.9       | Register Files                                 | 373 |

| Chapter 9 | Exercises                                      | 376 |

| 10        | Instruction Set Architecture                   | 381 |

| 10.1      | Instruction Set of a Computer                  | 382 |

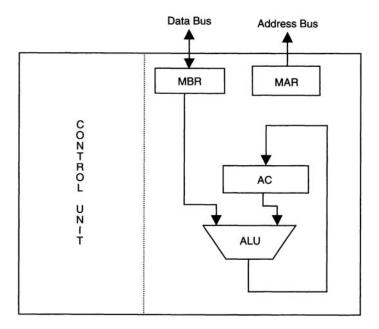

| 10.2      | Accumulator-Based Instruction Set Architecture | 383 |

| 10.2.1    | Accumulator-Based Architecture                 | 383 |

| 10.2.2    | Accumulator-Based Instructions                 | 384 |

| 10.2.2.1  | Load and Store Instructions                    | 385 |

| 10.2.2.2  | Arithmetic and Logic Instructions              | 385 |

| 10.2.2.3  | Register Transfer Languages                    | 387 |

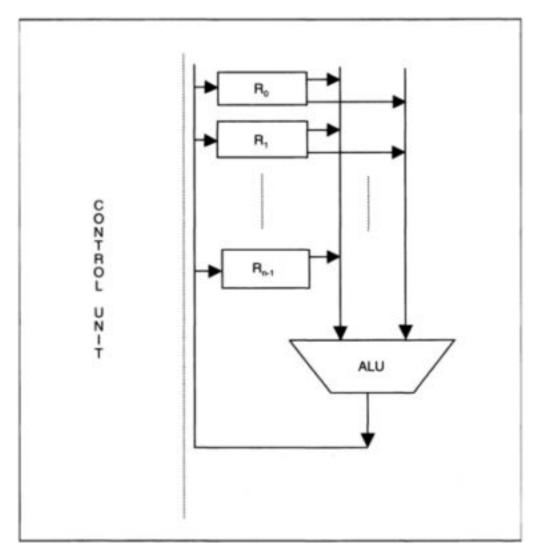

| 10.3      | General Register-Based Architecture            | 389 |

| 10.4      | Machine-Level Instructions                     | 391 |

| 10.5      | The Computer Instruction Cycles                | 394 |

| 10.6          | Common Addressing Modes                                      | 396 |

|---------------|--------------------------------------------------------------|-----|

| 10.7          | Macros                                                       | 401 |

| Chapter<br>10 | Exercises                                                    | 402 |

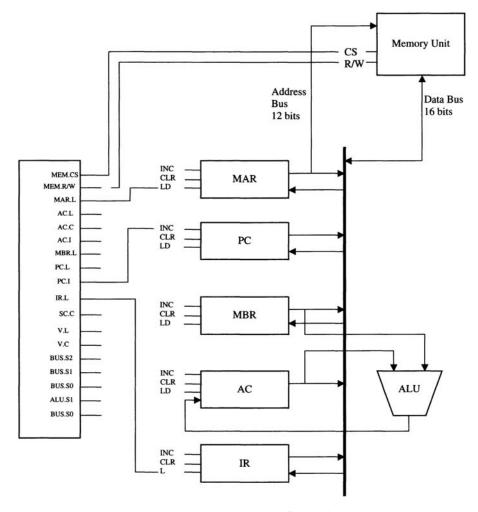

| 11            | Design of a Simple AC-Based CPU                              | 406 |

| 11.1          | Microoperation and Register Transfer Languages               | 407 |

| 11.2          | Design of RTL Statements                                     | 409 |

| 11.3          | Instruction Set of the Simple CPU                            | 414 |

| 11.3.1        | Instruction Set Completeness                                 | 414 |

| 11.3.1.1      | Arithmetic Instructions                                      | 414 |

| 11.3.1.2      | Logic Instructions                                           | 414 |

| 11.3.1.3      | Branch (Jump Instructions)                                   | 414 |

| 11.3.1.4      | CPU/and Memory Instructions                                  | 415 |

| 11.3.2        | The Instruction Set of the Simple CPU                        | 415 |

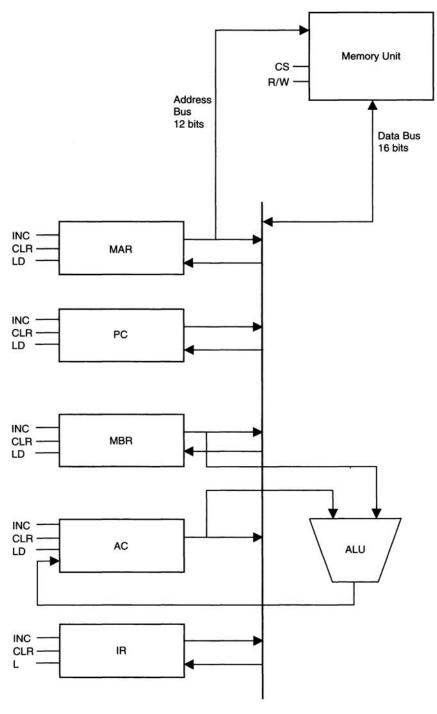

| 11.4          | CPU Organization Data Path                                   | 416 |

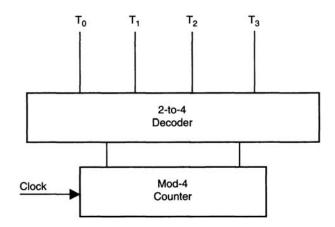

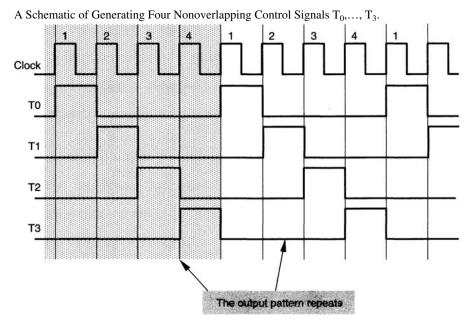

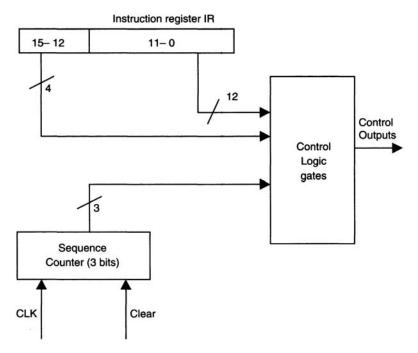

| 11.5          | The Control Unit                                             | 418 |

| 11.6          | The Three Cycles                                             | 421 |

| 11.7          | Computer Cycles Execute Microoperations                      | 422 |

| 11.7.1        | The Memory-Reference Instructions                            | 423 |

| 11.7.1.1      | The LW Instruction                                           | 423 |

| 11.7.1.2      | The ST Instruction                                           | 423 |

| 11.7.1.3      | The ADD Instruction                                          | 424 |

| 11.7.1.4      | The AND Instruction                                          | 424 |

| 11.7.1.5      | The JMP Instruction                                          | 424 |

| 11.7.1.6      | The SKZ and the SKP Instructions                             | 425 |

| 11.7.2        | Register-Reference Instructions                              | 425 |

| 11.8          | Inputs and Outputs of the Combinational Part of Control Unit | 426 |

| 11.8.1        | Input Part                                                   | 426 |

| 11.8.2        | Output Part                                                  | 427 |

| 11.9          | The Control Unit Output Functions                            | 428 |

| 11.10          | Design of the AC-Based CPU   | 431 |

|----------------|------------------------------|-----|

| Chapter<br>11  | Exercises                    | 432 |

| Appendi<br>x A | References                   | 436 |

| Appendi<br>x B | Answers to Selected Problems | 438 |

| Index          |                              | 462 |

## **1** Numbers in Different Bases

#### CONTENTS

| 1.1   | Digital and Analog Data                                                | 2  |

|-------|------------------------------------------------------------------------|----|

| 1.2   | Coding                                                                 | 3  |

| 1.3   | Positional Number System                                               | 4  |

| 1.3.1 | Numbers without Radix Point                                            | 4  |

| 1.3.2 | Numbers with Radix Point                                               | 5  |

| 1.4   | Octal and Hexadecimal Bases                                            | 6  |

| 1.5   | Operands Types and Their Range                                         | 10 |

| 1.5.1 | Data Types                                                             | 10 |

| 1.5.2 | Finite Range                                                           | 10 |

| 1.6   | Conversion of Decimal Numbers to Equivalent Numbers in Arbitrary Bases | 12 |

| 1.6.1 | Conversion of Integer Part                                             | 13 |

| 1.6.2 | Converting the Fractional Part                                         | 14 |

| 1.7       | Binary Arithmetic                                   | 16 |

|-----------|-----------------------------------------------------|----|

| 1.7.1     | Addition                                            | 16 |

| 1.7.2     | Subtraction                                         | 19 |

| 1.7.3     | Multiplication                                      | 20 |

| 1.8       | Radix and Diminished Radix Complements              | 22 |

| 1.9       | Representation of Negative Numbers                  | 24 |

| 1.9.1     | The Three Representations                           | 24 |

| 1.9.2     | Range of the Numbers                                | 26 |

| 1.10      | Coding and Binary Codes                             | 27 |

| 1.10.1    | BCD Code                                            | 28 |

| 1.10.2    | The Excess-m Code                                   | 29 |

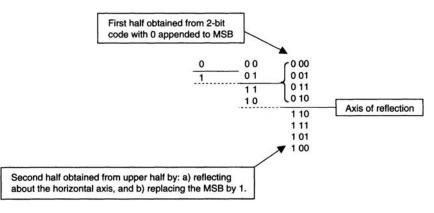

| 1.10.3    | Gray Code                                           | 30 |

| 1.10.4    | Character Codes                                     | 31 |

| 1.11      | Floating-Point Numbers                              | 32 |

| 1.11.1    | Binary Representation of Floating-Point             | 32 |

| 1.11.2    | Normalized and Biased Floating-Point Representation | 34 |

| Chapter 1 | Exercises                                           | 35 |

#### 1.1 Digital and Analog Data

This textbook is about the principle of digital computer design. The term "digital" is a characterization of data in a set. We say a set of data is digital if it contains a finite set of elements. Examples of digital data are the sets  $\{0, 1\}$ ,  $\{\text{on}, \text{off}\}$ ,  $\{\text{red}, \text{blue}, \text{green}\}$ , and  $\{x: x \text{ is a decimal digit}\}$ . In each of the examples, the set of data is digital since the number of elements in the set is finite.

The set of data is analog if the set contains a continuous interval of data elements. As a result, the set of data contains infinite number of elements since continuous intervals contain infinite data elements. Examples of analog data are the set of real numbers, the set of all colors, and the set of real numbers between 0 and 10.

We often approximate analog data by converting the data into digital format. For example, time is analog. When communicating time, we usually give time in hours and minutes. An example is the time display on computer monitors.

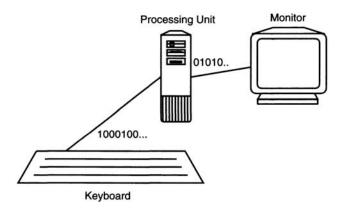

#### **FIGURE 1.2.1**

A Computer with a Keyboard, Processing Unit, and Monitor

Our discussion of digital design relates to digital computers. As the name implies, computers are digital, which means they process digital data. In addition, computers are programmable, i.e., the computer can be instructed to perform specific tasks according to a user, the programmer. The program is stored in the computer in digital format. The format is a sequence of 0 and 1 digits called bits.

### 1.2

#### Coding

Consider the schematic given in Figure 1.2.1 of a computer with a keyboard, a processing unit, and a monitor. When programming, the user may enter the program or data using the keyboard.

Note that the set that contains all keyboard data is digital since it contains a finite set of elements.

Since the computer processes binary data (data composed of 0s and 1s), the following three steps occur:

- The keyboard data is encoded into a sequence of bits where letters, digits, and other symbols are assigned a binary code, code word. Encoding is a mapping that associates with each object in some set a unique element (code word) in some other set. In this case, the set of objects is the set of keyboard data. We would like to associate a binary code sequence with all keyboard data.

- 2. The second step in this process is for the computer to perform the needed task. This occurs in the central processing unit (CPU), which includes special electrical circuits that accomplish these tasks.

#### **FIGURE 1.2.2**

The Three Steps of Encoding, Processing, and Decoding

3. The last step is to convert the binary results back into user format, for example, in decimal digits and alphabets. This step is called decoding and is the reverse of encoding. Figure 1.2.2 shows the three steps.

Discussing the details of the three steps is the subject of this text. Since computers process binary data, this will be our starting point.

#### 1.3 Positional Number System

In positional number systems, a number, N, is characterized by a base, b, also called a radix, and the coefficients (0, 1, ..., (b-1)) that make up the number. In decimal numbers (base 10), the base is implicit and can be omitted if needed. When other bases are considered, the base is explicitly identified in the representation as  $(N)_{b_1}$  or  $N_{b_2}$  where b is the base.

For example, in base 10 the coefficients of N are 0, 1, ..., 9. Similarly, in base 5 the coefficients of the number are 0, 1, 2, 3, and 4, and for base 16 the coefficients of the number are the decimal digits 0 through 9 and the letters of the alphabet A, B, C, D, E, and F, representing the decimal numbers 10, 11, 12, 13, 14, and 15, respectively. The symbols are needed since the base of the number exceeds base 10. The first six letters of the alphabet are customarily used in addition to the ten decimal digits.

We consider two formats, numbers with no radix point and numbers with radix (decimal) points.

#### 1.3.1 Numbers without Radix Point

For a given number  $(N)_b = n_i n_{(i-1)} \dots n_0$  in some base, *b*, the expanded polynomial representation of the number is

$$(N)_{b} = n_{i} \times b^{i} + n_{(i-1)} \times b^{(i-1)} + n_{(i-2)} \times b^{(i-2)} + \dots + n_{0} \times b^{0}$$

The expanded representation is used to convert a number, in an arbitrary base, to the equivalent representation in base 10. The following three examples make use of the above equation.

#### Example 1.3.1

- 1. Write the decimal number 1023 in expanded form according to the format given above.

- 2. Find the base 10 values of

i. (1023)<sub>5</sub> ii. (10111)<sub>2</sub> iii. (23AF)<sub>16</sub>

**Solution of part 1:** The number is composed of four digits with b=10 and i=3. Hence, using the equation above, we have  $n_3=1$ ,  $n_2=0$ ,  $n_1=2$ , and  $n_0=3$ . The expanded number is obtained by substituting these values above to obtain (1023)  ${}_{10}=1\times10^3+0\times10^2+2\times10^1+3\times10^0$

#### Solution of part 2:

1. Here, we have i=3 and b=5. Hence  $(1023)_5=1\times5^3+0\times5^2+2\times5^1+3\times5^0$  =125+0+10+3=(138)\_{10}

2.

$$(10111)_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 1 \times 2^0$$

= 16+ 0+4+2+1=(23)<sub>10</sub>

3.  $(23AF)_{16} = (2 \times 16^3) + (3 \times 16^2) + (A \times 16^1) + (F \times 16^0)$

=  $(2 \times 16^3) + (3 \times 16^2) + (10 \times 16^1) + (15 \times 16^0)$

=  $8192 + 768 + 160 + 15 = (9135)_{10}$

#### 1.3.2 Numbers with Radix Point

A number, (N)b, with a radix point (similar to the decimal point) is represented as

$(N)_b = (n_i n_{(i-1)} \dots n_0 \cdot n_{-1} n_{-2} \dots n_{-m})_b$ with two parts: (1) the integer part  $n_i n_{(i-1)} \dots n_{0}$ , and (2) the fractional part  $n_{-1} n_{-2} \dots n_{-m}$ . The subscripts correspond to the location of a given digit relative to the radix point. The subscripts of the whole part start with 0, while the subscripts for the fractional part start with -1. For base 10, the radix point is called a decimal point. For base 2, the radix point is called a binary point. For a given number in some arbitrary base, b, the equivalent decimal number is obtained by adding all the digits of the number after multiplying each by  $b^i$ , where i is the position of the digit.

#### Example 1.3.2

Find the equivalent decimal number for:

1.  $(1023.21)_5$ 2.  $(10111.01)_2$

Solution: Using the procedure listed above for part 1, we obtain  $(1023.21)_5 = 1 \times 5^3 + 0 \times 5^2 + 2 \times 5^1 + 3 \times 5^0 + 2 \times 5$   $^{-1}+1 \times 5^{-2} = 125 + 0 + 10 + 3 + 2/5 + 1/25 = (138.44)_{10}$ For part 2, we obtain  $(10111.01)_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 1 \times 20$  $+0 \times 2^{-1} + 1 \times 2^{-2} = 16 + 0 + 4 + 2 + 1 + 0 + 1/4 = (23.25)_{10}$

Commonly used bases in digital design and machine level programming are base 2, base 8, and base 16, referred to as binary, octal, and hexadecimal bases, respectively. We next discuss the conversion process between the three bases.

#### 1.4

#### **Octal and Hexadecimal Bases**

Octal and hexadecimal bases are used to make the translation process between the user and the computer easier. Computers process binary information. In addition to data, programs that instruct the computer what to do are also represented in binary format. Early computer designers and programmers found that it is hard to recognize the meaning of instructions from their binary representations. In addition to the length of a binary pattern, it is hard to distinguish one binary pattern from another. Hence, it is difficult to distinguish one computer instruction from another when instructions are given in binary format. The use of the base 8 (octal base) and base 16 (hexadecimal base) simplifies this process. The process of conversion between the three different bases is discussed next. We first introduce some terminology.

The individual digits of a binary number are called bits. An *n*-bit number is a binary number that is composed of *n* bits. The most-significant digit (MSD) is the left-most digit (for binary numbers, it is called most-significant bit (MSB)). Similarly, the least-significant digit (LSD) is the right-most digit of the number (in the case of binary numbers, it is called least-significant bit (LSB)).

To convert a binary number to octal:

- 1. Group the binary numbers into sets of three bits. The reference point used is the binary point. For the integer part, in grouping the number we move from the binary point to the left; for the fractional part we move from the binary point to the right.

- 2. If needed, we append zeros on the left of the integer part (the MSB) and zeros on the right of the fractional part (the LSB), respectively. This is done to form complete groups of 3 bits.

- 3. Replace each group formed in 1 and 2 with its equivalent octal number.

Note that appending zeros on the left of the integer part and/or on the right of the fractional part does not change the value of the original number.

To convert a binary number to hexadecimal we follow the procedure listed above; however, the bits are grouped into groups of 4 bits.

To accomplish step 3 in the above procedure, we use Table 1.4.1(a) and (b). The following examples illustrate the use of the procedure outlined above.

#### **TABLE 1.4.1** (a)

| Binary | Octal Equivalent |  |

|--------|------------------|--|

| 000    | 0                |  |

| 001    | 1                |  |

| 010    | 2                |  |

| 011    | 3                |  |

| 100    | 4                |  |

| 101    | 5                |  |

| 110    | 6                |  |

| 111    | 7                |  |

#### **TABLE 1.4.1(b)**

Used to Convert 4-Bit Binary Number to Equivalent Hexadecimal Digit

| Binary Number | Decimal Equivalent | Hexadecimal Equivalent |

|---------------|--------------------|------------------------|

| 0000          | 0                  | 0                      |

| 0001          | 1                  | 1                      |

| 0010          | 2                  | 2                      |

| 0011          | 3                  | 3                      |

| 0100          | 4                  | 4                      |

| 0101          | 5                  | 5                      |

| 0110          | 6                  | 6                      |

| 0111          | 7                  | 7                      |

| 1000          | 8                  | 8                      |

| 1001          | 9                  | 9                      |

|               |                    |                        |

| Binary Number | Decimal Equivalent | Hexadecimal Equivalent |

|---------------|--------------------|------------------------|

| 1010          | 10                 | А                      |

| 1011          | 11                 | В                      |

| 1100          | 12                 | С                      |

| 1101          | 13                 | D                      |

| 1110          | 14                 | E                      |

| 1111          | 15                 | F                      |

#### Example 1.4.1

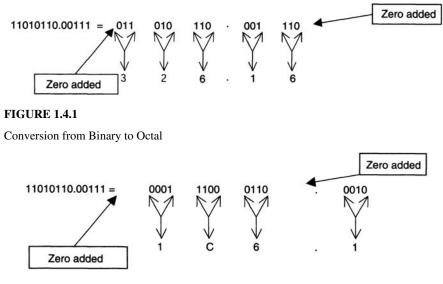

Convert the binary number 11010110.00111 into octal representation.

On grouping the binary digits into groups of three, we note that we need to append a zero on the left-hand side of the whole part and a zero on the right-hand side of the fractional part. The modified number, the grouping, and the equivalent octal number are given in Figure 1.4.1.

#### Example 1.4.2

Convert the binary number 111000110.001 into hexadecimal representation.

Similar to Example 1.4.1, on grouping the binary digits into groups of four, we note that we need to append three zeros on the left-hand side of the whole part

```

FIGURE 1.4.2

```

Conversion from Binary to Hexadecimal

and a zero on the right-hand side of the fractional part. The modified number, the grouping, and the equivalent hexadecimal number are given Figure 1.4.2.

Before we leave this section we note that the above process can be reversed, i.e., given a number in octal or hexadecimal form, one can find the binary equivalence by associating with each group the needed bit sequence. In addition, one can convert between the octal and hexadecimal bases by first converting the number into binary format; this can then be followed by the conversion as discussed above.

#### Example 1.4.3

Given the octal number  $(127.25)_8$ , find its hexadecimal equivalence.

**Solution:** We first convert the number into binary. The bits of the equivalent binary numbers are then grouped and the corresponding hexadecimal number is found accordingly:

$$(127.25)_{8} \xrightarrow{To Binary} \underbrace{0010101111}_{1} \underbrace{010101}_{2} \underbrace{11}_{7} \underbrace{010101}_{2} \underbrace{100101}_{5} \underbrace{10000}_{0} \underbrace{01010101}_{5} \underbrace{0111}_{7} \underbrace{010101}_{5} \underbrace{0100}_{4}$$

$$= (57.54)_{16}$$

#### 1.5

#### **Operands Types and Their Range**

We start our discussion by considering data types as related to programming languages and mathematics.

### TABLE 1.5.1

Data Types

| Computer Data Type | Mathematics Equivalent Type | Examples             |

|--------------------|-----------------------------|----------------------|

| Unsigned           | Natural numbers             | 0, 5, 10             |

| Signed             | Integers                    | -5, 0, 1, 6          |

| Fixed-point        | Rational                    | 1.2, 1.5             |

| Floating-point     | Rational                    | $-2.1 \times 10^{5}$ |

| Character          | -                           | 'A'                  |

#### 1.5.1 Data Types

In mathematics we characterize numbers in terms of their set of possible values. In particular, the characterization includes the sets of natural numbers, integer numbers, rational numbers, real numbers, and complex numbers. This characterization is carried into computer representation of numbers. This is done in programming languages, for example, under the variable declaration part. Here, the concept of a variable of a certain data type is important. In computer arithmetic we consider the representations shown in Table 1.5.1.

In computer arithmetic, with the exception of the last row, we deal with the data types listed in column 1. We assume unsigned integers to mean nonnegative integers (no sign is associated with the number); signed integers represent both positive and negative integers. The remaining two representations are used to approximate real numbers. Fixed-point representations include integers (signed or unsigned) with a radix point that separates two parts, the integer part and the fractional part. Floating-point representation is composed of two parts as well, a fixed-point part and a base-exponent part. For example,  $-2.1 \times 10^5$  contains two parts, -2.1 is the fixed-point part and  $10^5$  is the base-exponent part. We will say more about the representation later in the chapter.

#### 1.5.2 Finite Range

Mathematics uses sets with infinite cardinality (the cardinality of a set is the number of elements in the set). Computers contain finite storage elements. As a result, computers process only subsets of such sets. When arithmetic is performed on operands (numbers), it is stored in registers having a finite number

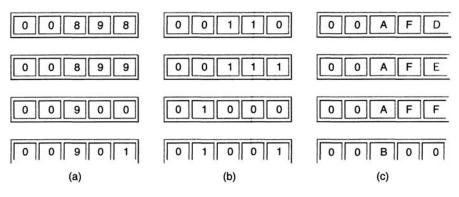

**FIGURE 1.5.1**

Counting in Different Bases

of storage elements. A register is characterized by the number of bits it contains. An n-bit register contains n storage elements; each element can store a bit for a total of n-bits. The finite number of bits limits the range of numbers that can be stored in the registers.

We relate our discussion to the odometer of a car in the case of storing decimal digits. The number of digits in the odometer is finite in size. As a result, the range of values that can be stored (recorded) is finite as well. For the case of an odometer with 5 decimal digits, the range of numbers is from the smallest, 00000, to the largest,  $99999=10^{5}-1$ . This yields a total of  $10^{5}$  numbers. The numbers stored are unsigned. In the odometer analogy, numbers in computers are stored in registers of finite size.

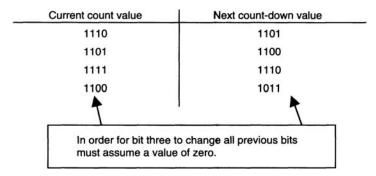

We relate the range of numbers in different bases to the process of counting in decimal. From this we conclude equations for the smallest and largest numbers of a given base.

In counting, the least-significant digit always changes. This digit is incremented until it reaches its maximum value (9). The maximum value is 1 less than the base, *b*. The next count causes the least-significant digit to change to 0. The next digit, however, is changed as well. In general, for a particular digit to change (be incremented or reset to 0), all preceding digits must assume their maximum value, b-1. In base 10, this occurs when all previous digits assume the value 9. In binary this occurs when all preceding digits assume a value of 1, as seen in Figure 1.5.1(b), rows 2 and 3. And, in hexadecimal this occurs when all preceding digits assume a value of F, as shown in Figure 1.5.1(c), rows 3 and 4.

In Figure 1.5.1(a), the range of values that can be stored is 0 through 99999  $(10^5-1)$  since the number of digits used is 5. Storing numbers outside this range causes an error called overflow if the number is larger than 99999. Similarly, if the number is smaller than 0, then an error called underflow occurs.

In general, the largest unsigned number that we could store in an n-bit register storing digits in base b is  $b^n-1$ . For counting in binary using an n-bit register, the

largest unsigned integer that can be stored is equal to  $2^n$ -1. For example, for 3-, 4-, and 5-bit register one can store unsigned binary integers in the range (000)<sub>2</sub> to (111)<sub>2</sub>=7, (0000)<sub>2</sub> to (1111)<sub>2</sub>=15 and (00000)<sub>2</sub> to (1111)<sub>2</sub>=31, respectively.

The range of the numbers changes if the number is stored in fixed-point format. For fixed-point format, we need to include the location of the radix point. The common locations of the radix point are at the right-most location of the register or at the left-most location, yielding an integer number and a fractional number, respectively. If the contents of an n-bit register represent a fraction, then the smallest range corresponds to 0 (all bits are 0). For the largest range we have

$$(a_{-1}a_{-2}a_{-3}a_{-4}\dots a_{-m})_2 = \left(\underbrace{1111\dots 1}_{m}\right)_2$$

$$= 2^{-1} + 2^{-2} + 2^{-3} + 2^{-4}\dots 2^{-m}$$

$$= 2^{-m} \left(2^{(m-1)} + 2^{(m-2)} + 2^{(m-3)} + \dots + 2^0\right)$$

$$= \frac{2^m - 1}{2^m}$$

$$= 1 - 2^{-m}$$

Hence, the 3-bit number,  $(111)_2$ , can be interpreted as the unsigned decimal number 7 or the fractional number 7/8.

Before we move to the next section, we list common units of binary measurements. Some of the common units of measurements used in the text are (1) 1 k (kilo)= $2^{10}$ =1024 (approximately 1000); 1 M (mega)= $2^{20}$  and 1 G (giga) = $2^{30}$ . Finally, the size of a register can be given in terms of bytes, with a byte equaling 8 bits. Hence, a 4-byte register is a 32-bit register. The size of the register is sometimes referred to as word. Hence, a 32-bit register has a word size of 32 bits. The largest unsigned integer that can be stored in the register is  $2^{32}$ -1, which is approximately 4 G.

#### 1.6

#### Conversion of Decimal Numbers to Equivalent Numbers in Arbitrary Bases

Given the decimal number  $(N)_{10}=(n_in_{(i-1)}...n_0.n_{-1}n_{-2}...n_{-m})_{10}$ ; to find its equivalent number in a different base, we use two procedures applied to the integer and the fractional part of N.

#### 1.6.1 Conversion of Integer Part

The process of converting a decimal number with no fractional part into an equivalent number in some base, *b*, is given in Algorithm 1.

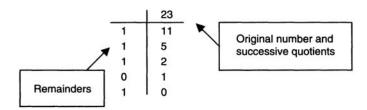

**Algorithm 1:** Given a decimal number, *N*, with no fractional part, the equivalent number in some base, *b*, can be obtained by repeatedly dividing the original number and all subsequent quotients by the base *b*. The remainders are saved in the order they are formed. The process terminates

| Remainders r <sub>i</sub> | Original Number (N) and Successive Quotients (qi) |

|---------------------------|---------------------------------------------------|

|                           | N=138                                             |

| · <sub>0</sub> =3         | <i>q</i> <sub>0</sub> =27                         |

| $r_0 = 3$<br>$r_1 = 2$    | <i>q</i> <sub>1</sub> =5                          |

| r <sub>2</sub> =0         | $q_2=1$                                           |

| r <sub>3</sub> =1         | $q_3=0$                                           |

when the final quotient obtained is 0. The equivalent number (in base b) is obtained by listing the remainders from least-significant digit to most-significant digit in the order they are formed.

The examples below illustrate the procedure outlined above.

TABLE 161

#### Example 1.6.1

Convert the decimal number  $(138)_{10}$  into an equivalent number in base 5.

We apply the procedure outlined earlier, as shown in Table 1.6.1. In this example, the original number, 138, is shown in the upper right. The reminder of division of 138 by 5 is  $r_0=3$ . The quotient  $(q_0)$  is 27 as listed. Row 3 in the table is obtained by repeating the division process, but by using the quotient, 27, instead of the original number. Finally, the last row is obtained by dividing the quotient 1  $(q_2=1)$  by 5 and saving the corresponding remainder and quotient in this row. Since the new quotient is 0, the process of conversion stops.

The remainders obtained (listed in the order formed and from right to left) constitute the equivalent number in base 5; that is

$$(138)_{10} = (1023)_5$$

Conversion from Base 10 to Binary (Whole Part)

# FIGURE 1.6.2

Conversion from Base 10 to Binary (Fractional Part)

# Example 1.6.2

Convert the decimal number 23 into an equivalent number in base 2. Using the procedure outlined in Algorithm 1, we obtain the results shown in Figure 1.6.1.

The binary number representation of the decimal number 23 is then given as

$(23)_{10} = (10111)_2$

# 1.6.2 Converting the Fractional Part

The process of converting the fractional part of a decimal number into an equivalent number in some arbitrary base, b, is obtained using Algorithm 2.

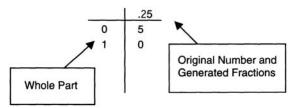

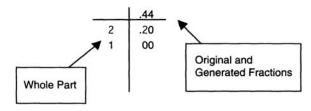

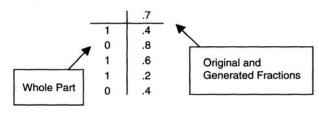

Algorithm 2: Repeatedly multiply the fractional part and all successively generated fractions by the base b with the integer result of each multiplication saved in the order it is formed. Continue until the fractional part value is 0. The fractional equivalent in base b is obtained by (1) listing the integer digits (in the order formed) from most significant (left) to least significant (right), and (2) appending a radix point on the left side of the number.

The examples below illustrate the use of Algorithm 2.

Converting  $(0.44)_{10}$  to Base 5

#### **FIGURE 1.6.4**

Converting  $(0.7)_{10}$  to Binary

#### Example 1.6.3

Convert the decimal fraction 0.25 to an equivalent fraction in base 2.

Applying Algorithm 2, we obtain the results in Figure 1.6.2. The original fraction, 0.25, is given in row 1. Row 2 contains two columns; the combined columns are the result of  $2^*$  (0.25). On multiplying the fraction 5 in row 2 by the number 2, we obtain the result shown in row 3. Since the updated fraction is 0, the algorithm terminates.

The equivalent fractional number in base 2 is obtained by (1) listing the whole parts from left to right in the order they are formed, and (2) appending a radix point to the left of the number. That is,

$(0.25)_{10} = (0.01)_2$

#### Example 1.6.4

Convert the fractional number  $(0.44)_{10}$  to an equivalent fraction in base 5.

Following the procedure outlined in Algorithm 2, we obtain the results in Figure 1.6.3, i.e.,  $(0.44)_{10}=(0.21)_5$ .

#### Example 1.6.5

Convert  $(0.7)_{10}$  to an equivalent binary fraction.

Figure 1.6.4 shows the conversion process. As was discussed earlier, the result in row 3 (0.8) is obtained from multiplying the fractional part in the previous row

(0.4) by 2. Now, referring to the last row, the fractional part under consideration is 0.4. As a result, on repeated multiplication of the generated fractions by 2, the sequence of whole digits obtained is (0110). This sequence is repeated indefinitely since the criteria for stopping the algorithm (a fraction of 0) cannot be satisfied.

The previous example points to an important fact about number conversions: some numbers are stored in the computer in an approximate and not-exact representation. (In mathematics, the equation x\*1/x=1 is always true when x is not equal to 0. This is not the case when testing the condition in programming languages.)

To convert a fixed-point decimal number to an equivalent number in arbitrary base, process the integer part and fractional parts as described above and combine the two parts.

#### Example 1.6.6

Convert  $(138.44)_{10}$  to the equivalent number in base 5.

From Examples 1.6.1 and 1.6.4, we have  $(138)_{10}=(1023)_{5}$ , and  $(0.44)_{10}=(0.21)_{5}$ . Combining the results yields  $(138.44)_{10}=(1023.21)_{5}$ .

#### 1.7

# **Binary Arithmetic**

In this section, we will discuss binary arithmetic with regard to the addition, subtraction, and multiplication operations as applied to unsigned integers and fixed-point numbers. We will first discuss decimal arithmetic. From this, we deduce arithmetic procedures on arbitrary.

# 1.7.1

#### Addition

In adding the decimal numbers A and B, we add the digits associated with the same location, including the carry that may be obtained from the previous location. The sum may require two digits to represent; this occurs if the sum exceeds 9 (1 less than the base value). The sum can be written as CS, with C the carry used into the next MSD of the sum. For example, the sum of the digits 7+5 is 12. Hence, C is 1 and S is 2. The C and S terms satisfy:

S=(X+Y) MOD b

C=(X+Y) DIV b

where *X* and *Y* are the two digits to be added, and *b* is the base. The MOD operation returns the remainder of (X+Y)/b while the DIV operation returns the quotient of the division.

In adding binary numbers, the individual digits used are 0 and 1. The result of adding two binary digits is given in Table 1.7.1. The table can be modified to include the addition of three binary digits. The modified table with a carry bit

included is given in Table 1.7.2. In adding two binary numbers, we use the above table to compute the intermediate steps.

| Addition of Two Binary Bits, Result Requires Two Bits C and S |     |   |  |  |  |

|---------------------------------------------------------------|-----|---|--|--|--|

| Original Digits                                               | Sum |   |  |  |  |

| A+B                                                           | С   | S |  |  |  |

| 0+0                                                           | 0   | 0 |  |  |  |

| 0+1                                                           | 0   | 1 |  |  |  |

| 1+0                                                           | 0   | 1 |  |  |  |

| 1+1                                                           | 1   | 0 |  |  |  |

#### **TABLE 1.7.1**

#### **TABLE 1.7.2**

Addition of Three Binary Bits, Result Requires Two Bits C and S

| Original Digits | Sum |   |

|-----------------|-----|---|

| Carry Digit+A+B | С   | S |

| 0+0+0           | 0   | 0 |

| 0+0+1           | 0   | 1 |

| 0+1+0           | 0   | 1 |

| 0+1+1           | 1   | 0 |

| 1+0+0           | 0   | 1 |

| 1+0+1           | 1   | 0 |

| 1+1+0           | 1   | 0 |

| 1+1+1           | 1   | 1 |

# Example 1.7.1

Add the two binary numbers 11011 and 11001.

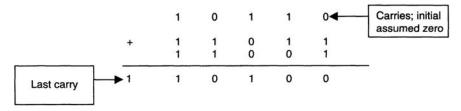

Using Table 1.7.2, we have the result shown in Figure 1.7.1.

The previous discussion can be applied to additions in arbitrary bases. The following example illustrates this for adding two numbers in base 5.

#### Example 1.7.2

Find x+y, where  $x=(123.4)_5$  and  $y=(241.1)_5$ .

We illustrate the process by adding individual digits and recording the sum in decimal; the sum can then be converted into two digits (in the CS form discussed above) in base 5.

The addition proceeds from right to left. In determining the sum, carries are recorded as well. The sum is shown in Table 1.7.3. The first column contains the carry-in and the digits of the two numbers listed from least significant to most

Addition of Two Binary Numbers 11011+110001, Upper Row Shows the Carries

significant. The sum in decimal is obtained from corresponding row digits (this includes the carry-in digits). The initial carry-in digit is 0. The remaining carries are obtained from converting the decimal sum into base 5. For example, the first row produces a decimal sum of 5, which is converted to  $(10)_5$ . The carry of 1 is moved to the next row, and the process of addition is repeated on this row.

## **TABLE 1.7.3**

| Carry+x+y | Sum in Decimal | Sum in Base 5 |   |  |  |  |

|-----------|----------------|---------------|---|--|--|--|

| С         | S              |               |   |  |  |  |

| 0+4+1     | 5              | 1             | 0 |  |  |  |

| 1+3+1     | 5              | 1             | 0 |  |  |  |

| 1+2+4     | 7              | 1             | 2 |  |  |  |

| 1+1+2     | 4              | 0             | 4 |  |  |  |

# **TABLE 1.7.4**

```

Base 16 Addition, 2397A.4+95CB.2

```

| Carry+x+y | Sum in Decimal | Sum in Base 16 |   |  |

|-----------|----------------|----------------|---|--|

| С         | S              |                |   |  |

| 0+4+2     | 6              | 0              | 6 |  |

| 0+A+B 21  |                | 1              | 5 |  |

| 1+7+C     | 20             | 1              | 4 |  |

| 1+9+5 15  |                | 0              | F |  |

| 0+3+9 12  |                | 0              | С |  |

| 0+2+0     | 2              | 0              | 2 |  |

The sum of the two numbers is obtained from the last column after including the radix point; the sum obtained is  $(420.0)_5$ .

Decimal Subtraction

#### Example 1.7.3

The sum *x*+*y*, where  $x=(2397A.4)_{16}$  and  $y=(95CB.2)_{16}$  is given in Table 1.7.4. From Table 1.7.4,  $(2397A.4)_{16}+(95CB.2)_{16}=(2CF45.6)_{16}$ . Note the added zero in the last row of the column with label *y*.

# 1.7.2 Subtraction

The process of subtraction in arbitrary base is derived from subtracting decimal numbers. We first illustrate by an example.

#### Example 1.7.4

Find  $(1230015)_{10}$ - $(1122124)_{10}$

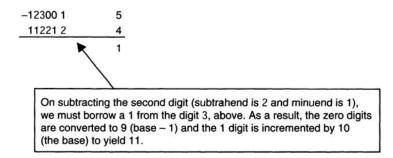

Using common subtractions on decimal, we make the text box note shown in Figure 1.7.2.

On applying the above, we get the result shown in Figure 1.7.3 with the updated and original digits as shown. The result of subtraction is also given. As can be seen from the figure, there are no additional borrows needed.

Note that in forming A-B, A is called the minuend and B is called the subtrahend.

The above rule can be generalized to subtract numbers in a different base, *b*. For a borrow, the zero digits to the left are changed to b-1, the digit that requires the borrow,  $a_i$  is changed to  $(a_i+_b)$ , and the digit that supplied the borrow,  $a_{(i+j)}$  is decremented by 1.

We consider the following examples to illustrate.

#### Example 1.7.5

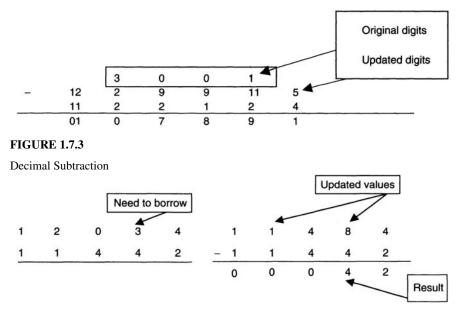

In this example we find  $(12034)_5 - (11442)_5$ .

Base 5 Subtraction, 12034-11442

The subtraction procedure is shown in Figure 1.7.4 using the steps outlined above.

#### Example 1.7.6

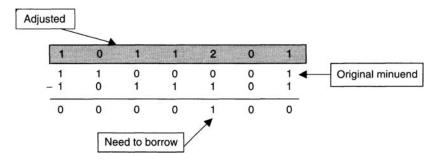

In this example, we find  $(1100001)_2 - (1011101)_2$ . Using the procedure, we obtain Figure 1.7.5.

#### Example 1.7.7

Find (1250A51)<sub>16</sub>-(1170F31)<sub>16</sub>.

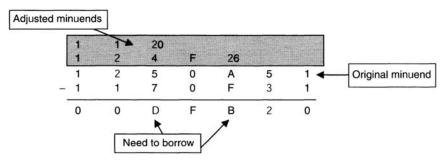

The result of the subtraction is shown in Figure 1.7.6.

The adjusted minuends are shown in the shaded area in Figure 1.7.6. The first row is the result of the first initiated borrow; the row above it is the result of the second initiated borrow.

# 1.7.3 Multiplication

We restrict the process of multiplication to binary, and illustrate the process by an example.

Base 2 Subtraction, 1100001-1011101

# **FIGURE 1.7.6**

Base 16 Subtraction, 1250A51-1170F31

#### Example 1.7.8

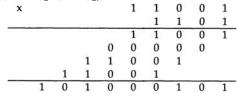

Form the product  $(11001)_2 \times (1101)_2$ .

Note that the multiplicand (11001) is copied as is if the bit in the multiplier (1101) is 1. It is replaced by a row of zeros if the multiplier bit is 0. The process is similar to regular multiplication. In regular multiplication, we form the partial products as shown in the rows above. Each partial product is properly shifted one bit position to the left. To obtain the product, we add all partial products as shown in the last row.

# 1.8 **Radix and Diminished Radix Complements**

The previous discussion dealt with number representations that are nonnegative. In the next section, we discuss representation of negative numbers. First, however, we discuss two forms of complements that are used in signed arithmetic, the diminished radix and radix complement representations.

The diminished radix representation of a number is determined from three parameters: the base, b, the number of digits in the number, n, and the number itself, N. For a number N, the diminished radix representation of the number is

$(b^n-1)-N$

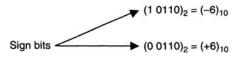

The representation is referred to as (b-1)'s complement. For example, in base 10, b=10, the representation is referred to as 9's complement. Similarly, in base 2 the diminished radix representation is referred to as 1's complement.

## Example 1.8.1

Form the 9's complement of the decimal number 123. **Solution:** Since *N*=123, the number of digits, *n*, is 3 and  $b^{n}-1=10^{3}-1=999$

(l

What is  $(b^{n}-1)$ ? From the above example, we note that  $(b^{n}-1)$  is a number with *n* digits, with each digit equal to b-1, i.e., to obtain the diminished radix complement of a number N, we subtract each digit in N from (b-1). The result is the desired diminished radix.

#### Example 1.8.2

In this example, we form the 1's complement of the binary number 10110.

Using the previous observation, we have

as the 1's complement of 10110.

Note that the diminished radix complement of a number is obtained from its individual digits. The sum of the digit and the corresponding digit in the diminished radix complement must add to (b-1). For the 1's complement case, we obtain the complement by complementing each bit of the number. For each bit in the number, the sum of the bit and the corresponding bit in the 1's complement must add to (b-1=1). We apply the rule on a different base, using the example below.

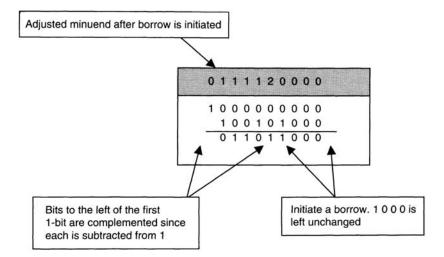

Forming 2's Complement. From the definition, no changes occur to the leftmost consecutive zeros in the number and first 1 bit that initiates the borrow. All remaining bits are complemented.

#### Example 1.8.3

Find the 4's complement of  $(1234)_5$ .

Using the above observation, the 4's complement is 3210 since

1+3=4, 2+2=4, 1+3=4, and 0+4=4

Similar to diminished radix complement, the radix complement representation is determined from three parameters: the base, b, the number of digits in the number, n, and the number itself, N. The representation is referred to as b's complement. It is called 10's complement in base 10 and 2's complement in base 2. For a number N, the radix complement representation of the number is

$$b$$

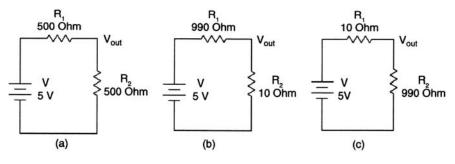

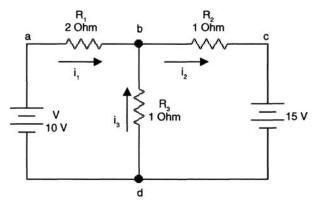

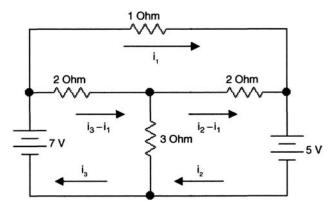

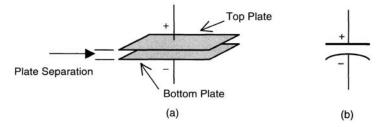

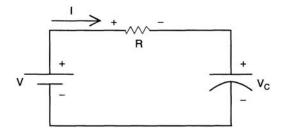

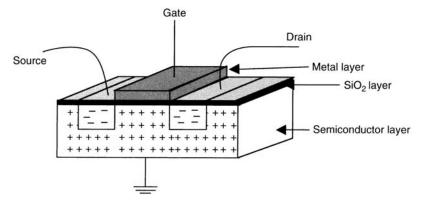

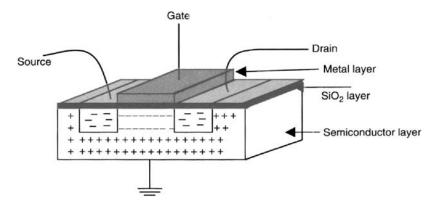

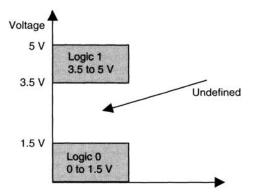

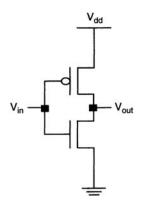

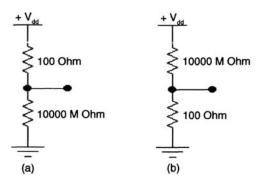

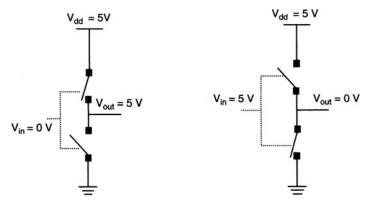

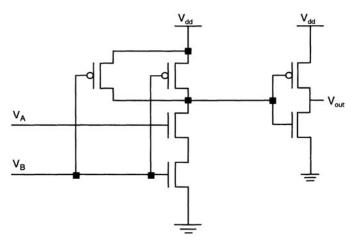

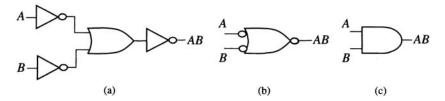

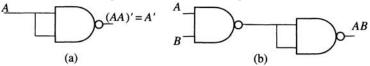

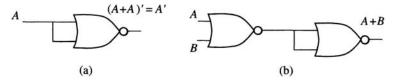

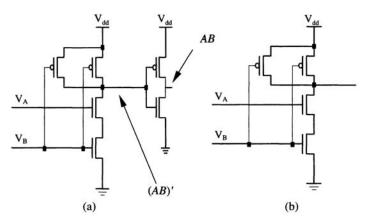

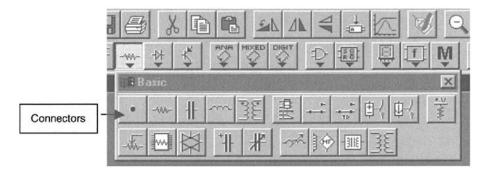

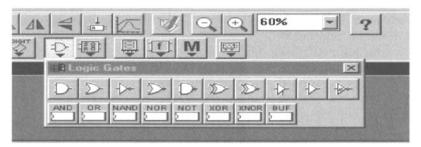

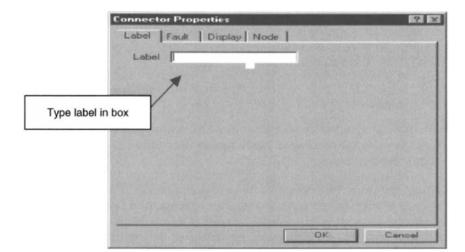

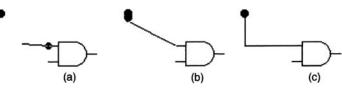

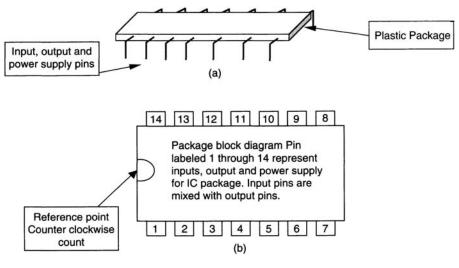

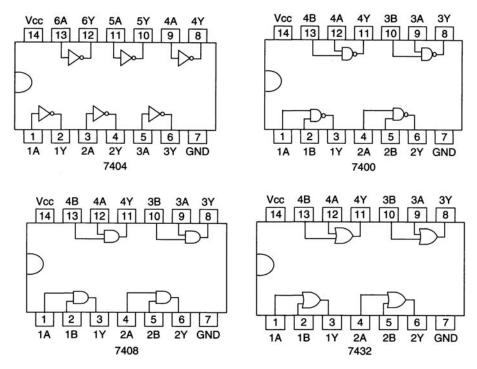

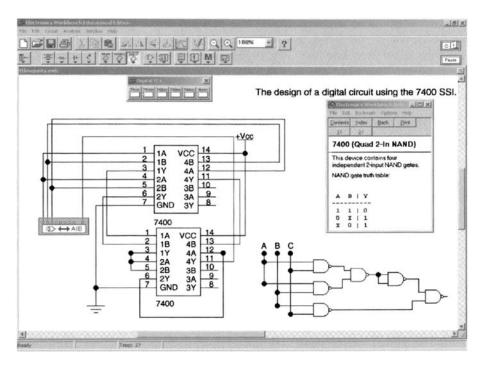

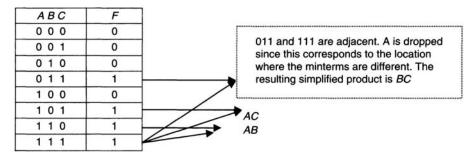

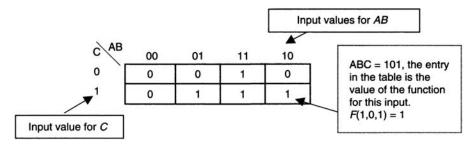

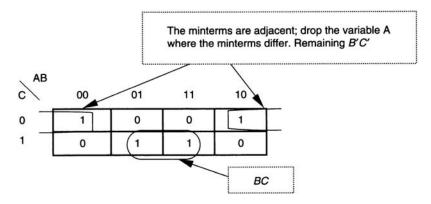

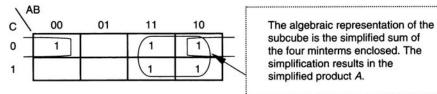

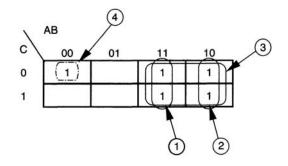

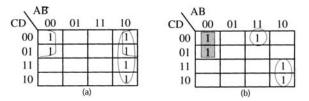

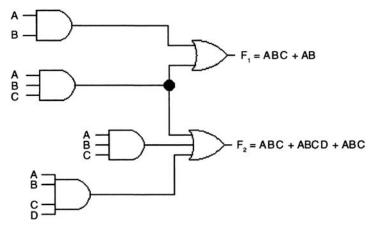

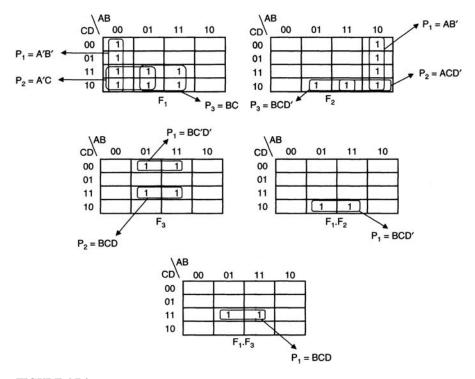

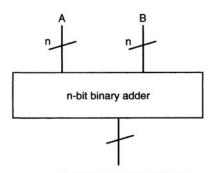

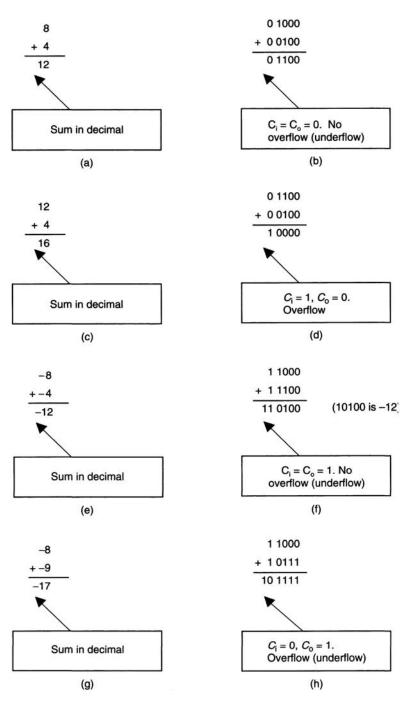

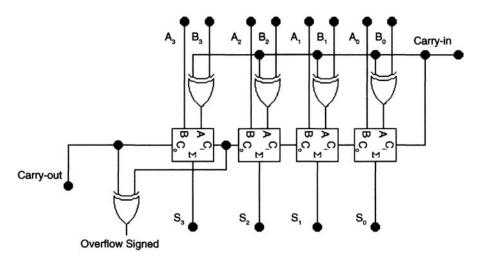

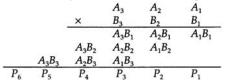

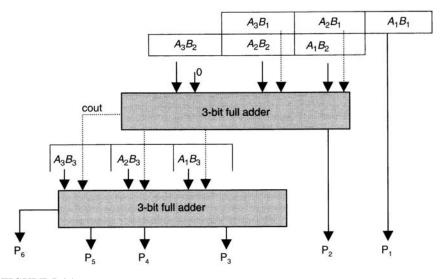

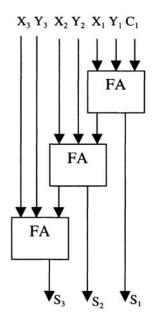

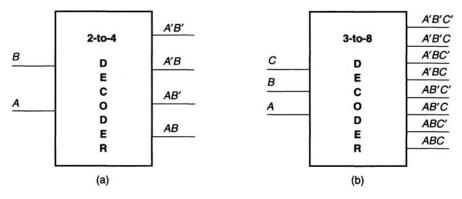

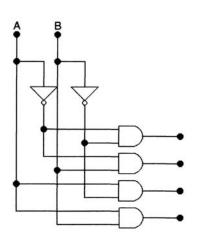

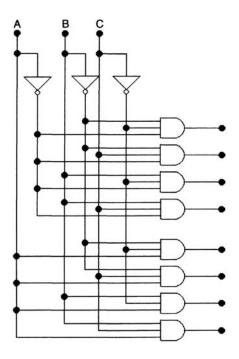

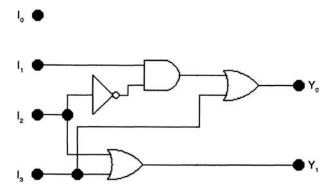

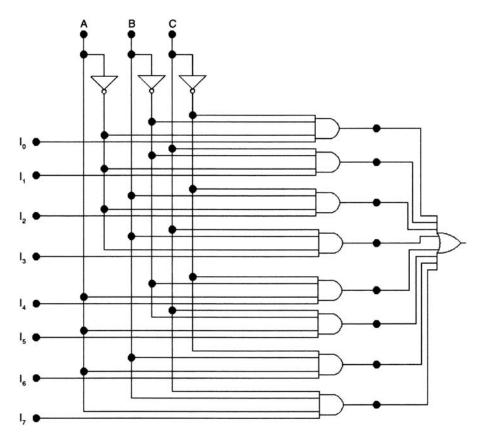

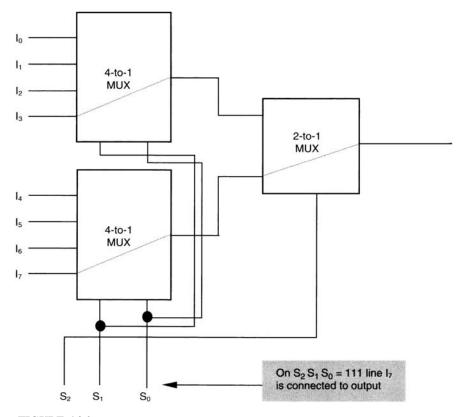

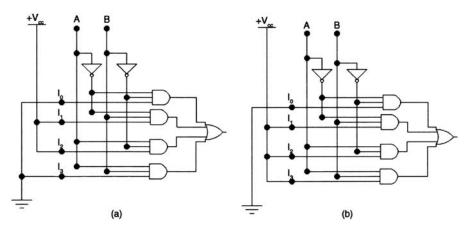

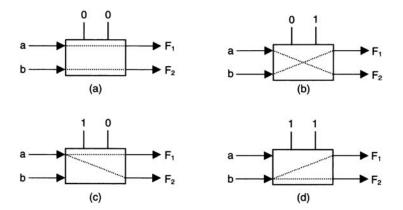

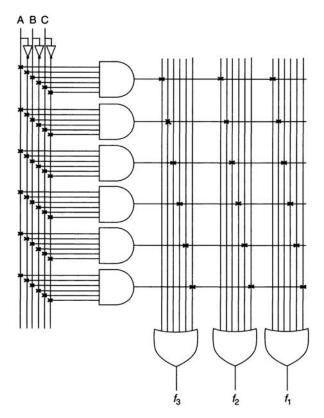

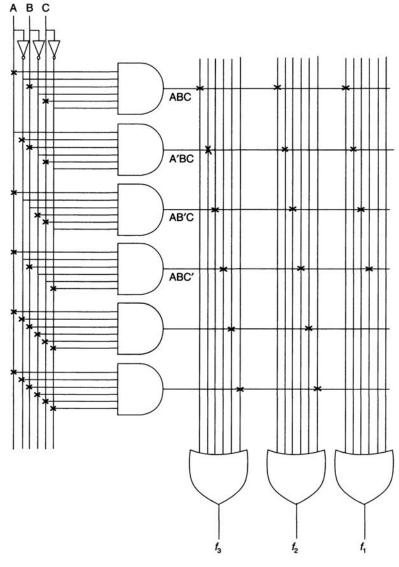

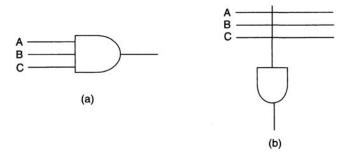

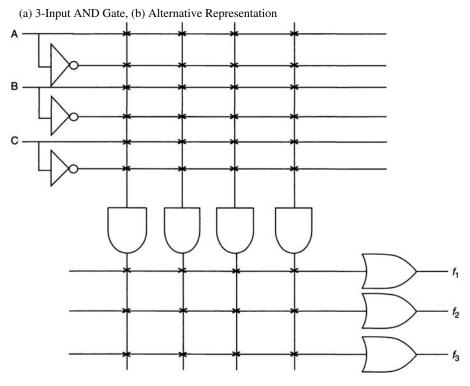

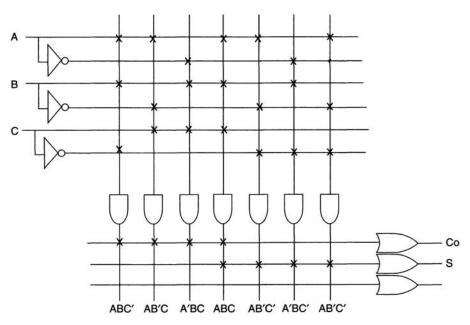

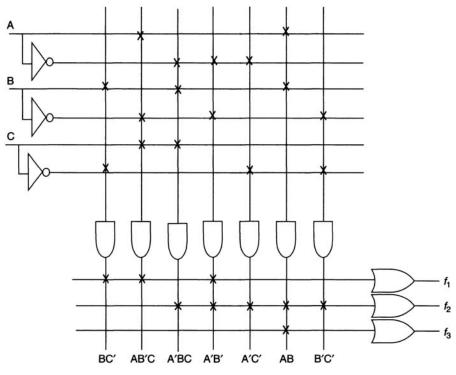

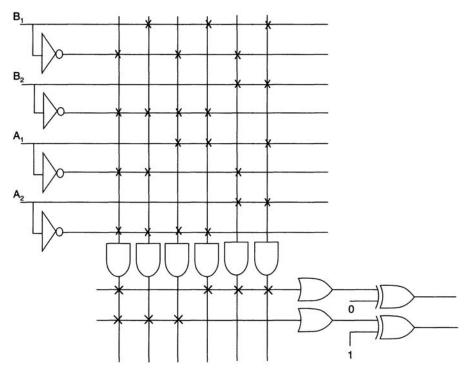

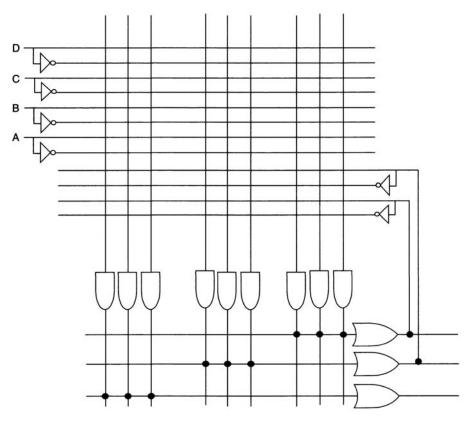

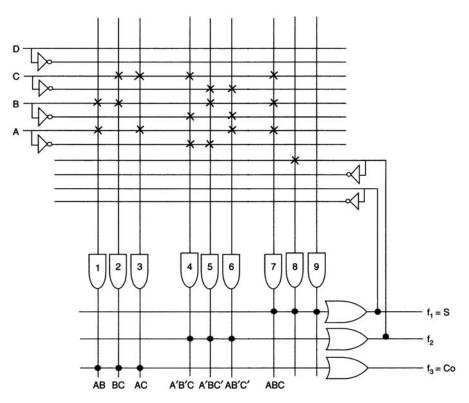

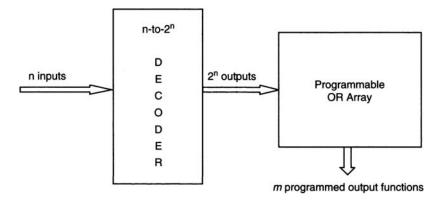

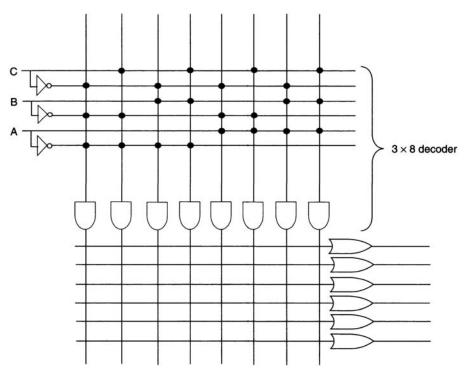

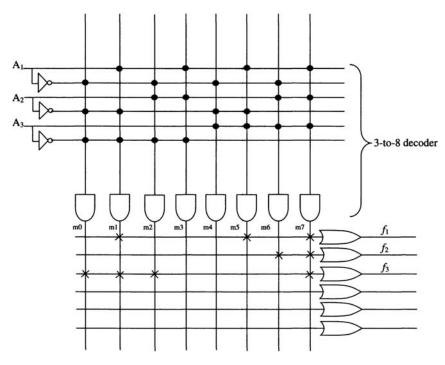

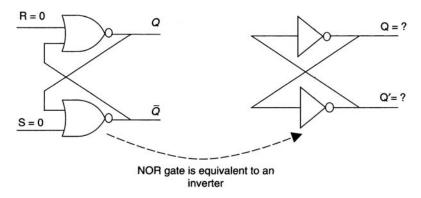

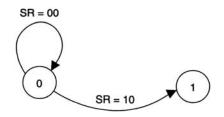

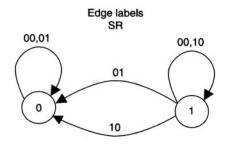

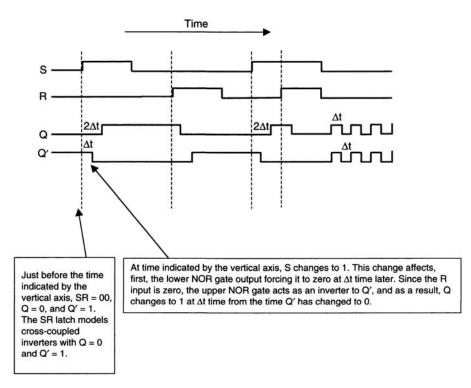

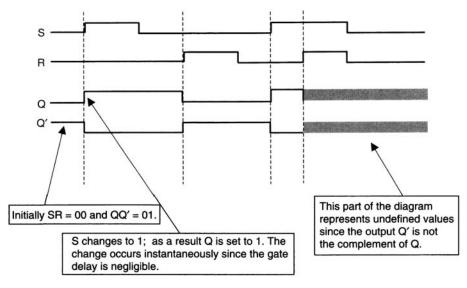

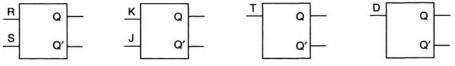

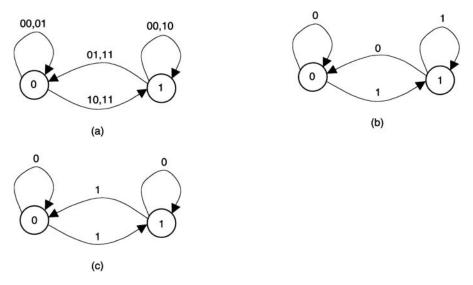

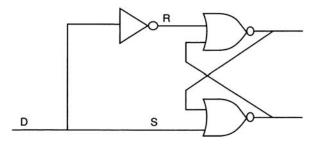

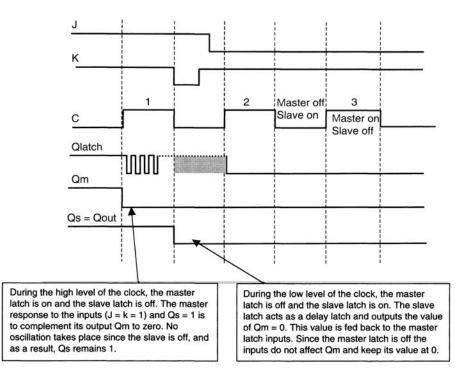

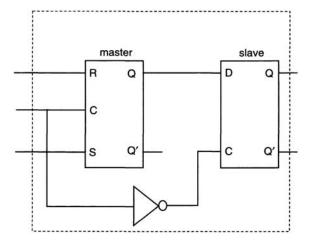

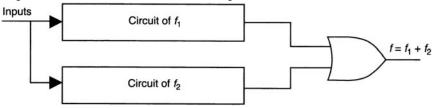

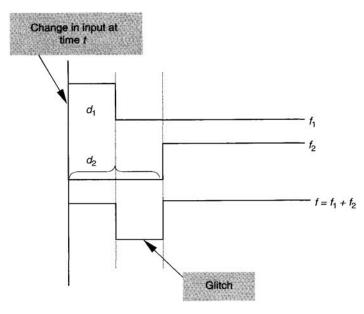

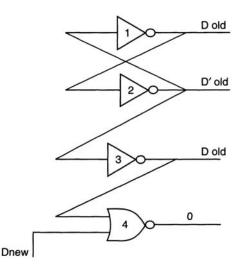

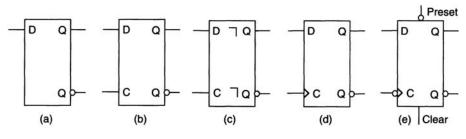

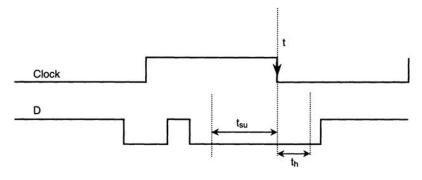

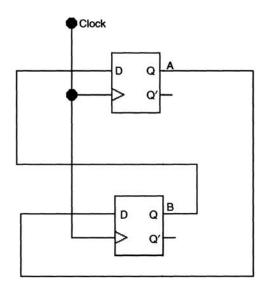

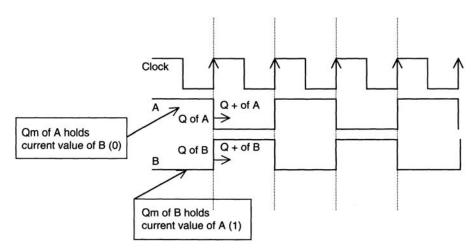

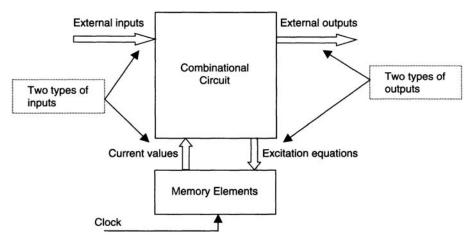

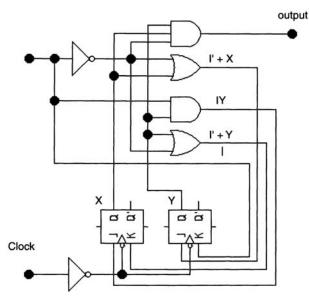

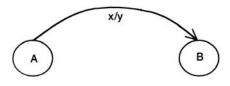

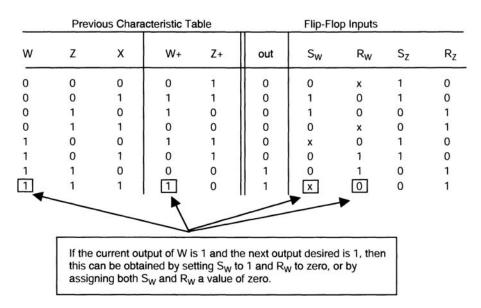

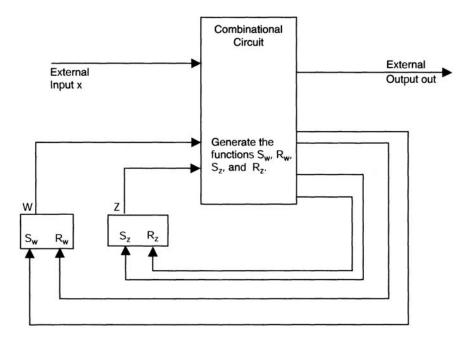

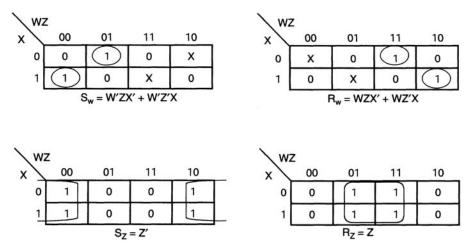

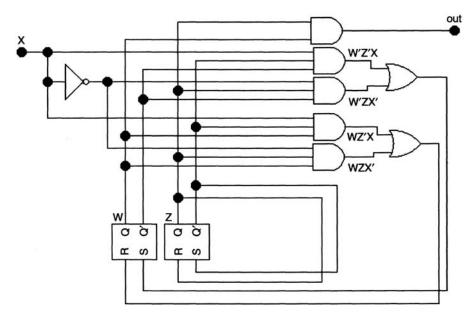

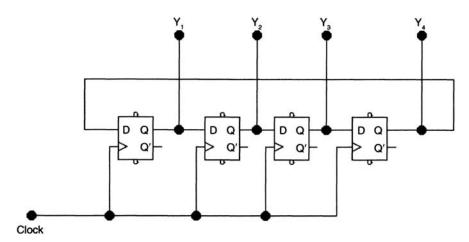

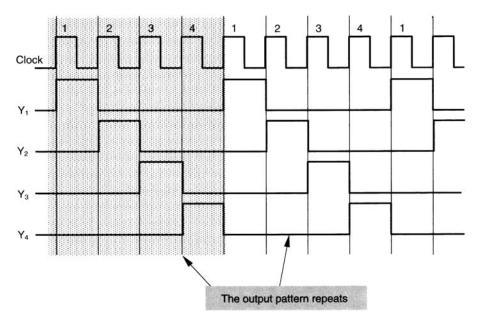

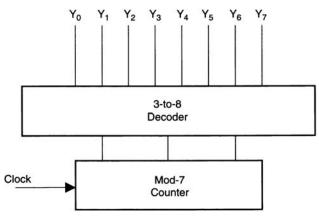

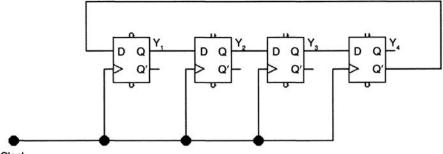

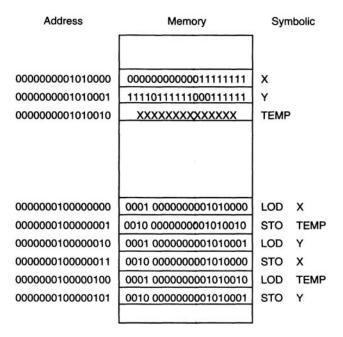

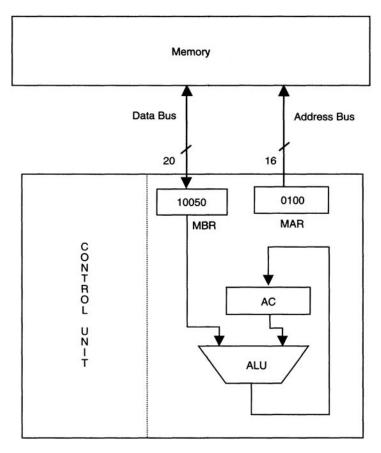

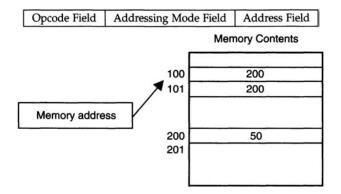

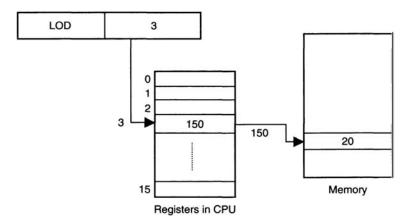

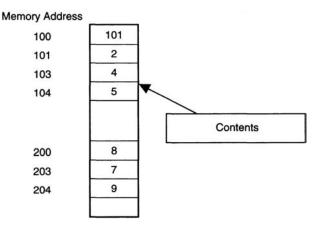

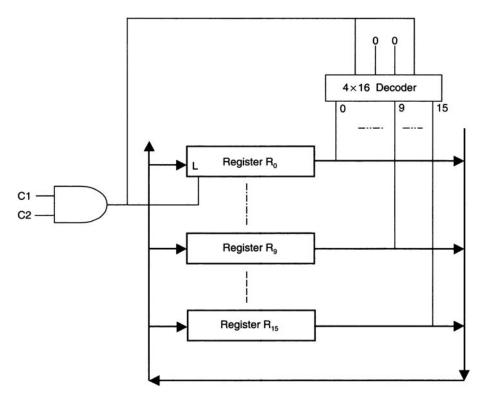

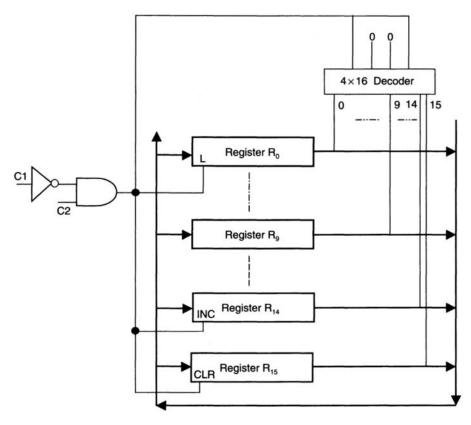

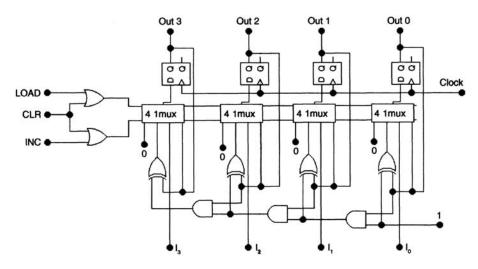

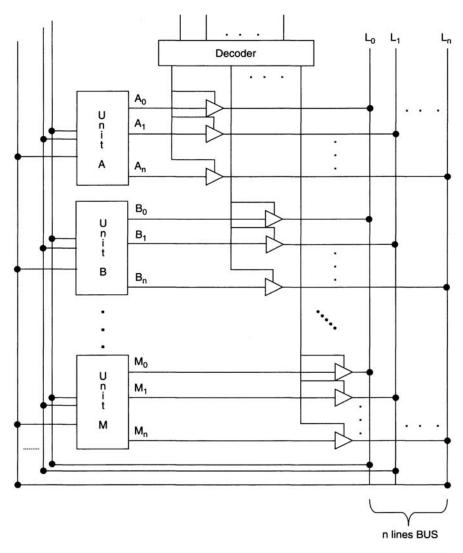

's complement =